課題番号 :F-21-NM-0003

利用形態 :機器利用

利用課題名(日本語) :ドット型脳型推論アナログ抵抗変化素子の作製

Program Title (English) : Fabrication of Resistive Analog Neuromorphic Device with Dot Structure

利用者名(日本語) :高橋慎

Username (English) : M. Takahashi

所属名(日本語) :国立研究開発法人 産業技術総合研究所

Affiliation (English) : National Institute of Advanced Industrial Science and Technology (AIST)

キーワード/Keyword:ナノエレクトロニクス、リソグラフィ・露光・描画装置、RAND、ReRAM

#### 1. 概要(Summary)

脳型推論アナログ抵抗変化素子 RAND(Resistive Analog Neuromorphic Device)は、優れた低消費電力性や高い集積化のポテンシャルに加えて、ディープラーニングをはじめとする AI 演算機構のハードウェア実装を実現するための素子として注目を集めている。本研究では RAND 素子の構造として、下部電極(BE)、ならびに上部電極(TE)と抵抗変化層の接触界面を同一面積にできるという利点を持つドット型構造を採用し、その作製プロセスを開発している。ドット型素子は TE とリードの接続のため、精密な頭出しが要求される。スリミングでドットサイズを微小化したため、頭出し工程で要求される高さ方向の精度が 20 nm 以下とシビアになったことから、化学機械研磨(Chemical Mechanical Polishing = CMP)による素子絶縁層平坦化後の頭出し工程の改良を行った。

#### 2. 実験(Experimental)

# 【利用した主な装置】

125kV電子ビーム描画装置、プラズマCVD装置、顕微式自動膜厚測定システム

#### 【実験方法】

産総研にて、熱酸化膜つき Si 基板上に BE 層、多層膜抵抗変化層、TE 層、転写マスク層を積層成膜した後、NIMS にて 125kV 電子ビーム描画装置でパターニング、エッチングしてドット型に成型加工した。さらに成型したドット型 RAND 素子に対し、プラズマ CVD 装置を用いて SiO2 絶縁層を 200 nm 成膜した。素子上の絶縁層の突起部を 外注作業にて CMP 平坦化した後、NIMS にて顕微式自動膜厚測定システムを用いて素子周囲の SiO2 残量を測定、産総研に持ち帰ってイオンミリング装置で SiO2 絶縁層をエッチング、これを繰り返して徐々に SiO2 を薄層化した。素子上部の TE 層である

TiN が露出した後は、産総研での原子間力顕微鏡 (Atomic Force Microscope = AFM) による測定に切り 替え、イオンミリング装置による nm 単位の精密な頭出し加工を行った。

# 3. 結果と考察(Results and Discussion)

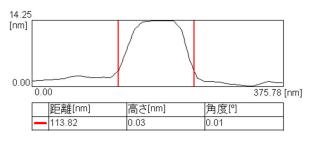

Fig. 1 に SiO<sub>2</sub> 絶縁層上に作製した頭出し後の RAND 素子の AFM による高さプロファイルを示す。

今回、RAND素子頭頂部が露出するまでは顕微式自動膜厚測定システムを用いて $SiO_2$ 残量を測定し、TE層である TiN が表面に出てからは AFM の高さ測定に切り替えたが、イオンミリングでは $SiO_2$ と TiN の選択比が 5 倍あるため、TiN 周囲の $SiO_2$  が優先的に加工されることで生じる段差の高さを AFM で評価できる。その結果をもとに、露出部の高さを  $10\sim15$  nm の間に制御することが可能である。

Fig. 1 AFM profile of RAND dot element on the SiO<sub>2</sub> insulating layer after exposing the top of the dot element by Ar ion milling process.

# 4. その他・特記事項(Others)

なし

# 5. 論文・学会発表 (Publication/Presentation)

### 6. 関連特許(Patent)

なし