課題番号 : F-20-UT-0050

利用形態 :技術補助

利用課題名(日本語) :経年劣化を抑制するスターブ型リングオシレータを搭載した集積回路の配線修正

Program Title (English) : Wire Fabrication of a Semiconductor Chip Embedding Staved Ring Oscillator to

Suppress Aging Degradation

利用者名(日本語) :岸田亮 1), 松本泰輔 1), 南出大輔 1), 小林和淑 2)

Username (English) : R. Kishida<sup>1)</sup>, T. Matsumoto<sup>1)</sup>, D. Minamide<sup>1)</sup>, K. Kobayashi<sup>2)</sup>

所属名(日本語) :1) 東京理科大学理工学部 2) 京都工芸繊維大学電子システム工学専攻

Affiliation (English) :1) Faculty of Science and Technology, Tokyo University of Science 2) Master's

Program of Electronics, Kyoto Institute of Technology

キーワード/Keyword:スターブ型リングオシレータ,集積回路,経年劣化,金属配線、切削、研磨、接合

### 1. 概要(Summary)

集積回路の信頼性は重要であり、その実測評価も重要である。信頼性を悪化させる要因の 1 つである経年劣化を抑制するために試作した集積回路の配線を修正する。 FIB により、金属配線を接合することで、回路に搭載されたスターブ型リングオシレータの発振周波数を実測評価する。

### 2. 実験(Experimental)

#### 【利用した主な装置】

・集積回路パターン微細加工(FIB)装置 V400ACE 【実験方法】

つながっていない金属配線を FIB により接続する. 修正した試作回路が正常動作することを FPGA により動作確認し, 試作回路を用いてリングオシレータの周波数を実測する. 65 nm プロセスの試作回路であり, 4 層目と7 層目にある電源線の金属配線を接続する.

## 3. 結果と考察 (Results and Discussion)

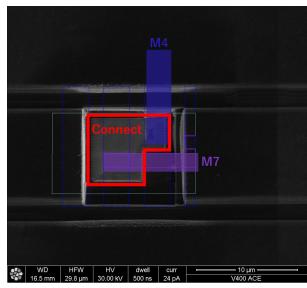

修正する前は正常動作しなかったが、FIB を用いた修正により、試作回路に搭載したシフトレジスタの値が期待値通りに出力されることを確認した。これにより、FIB による金属配線接続が正しく行われたことを確認した。Fig. 1に FIB 加工後の SIM (Scanning Ion Microscope) 像を示す。接続されていなかった金属配線が接続されている。

回路に搭載したスターブ型リングオシレータの発振周 波数の経年劣化を測定することで, 搭載した回路が経年 劣化を抑制できることを確認した.

#### <u>4. その他・特記事項(Others)</u>

謝辞:FIB の技術補助をしてくださったネクスティエレクトロニクスの木下純様ならびに東大微細加工拠点の学術支援専門職員太田悦子氏に深く感謝いたします.

Fig. 1: SIM image of the chip after FIB fabrication. Metal wires of M4 and M7 are boded each other.

# 5. 論文・学会発表 (Publication/Presentation)なし.

# 6. 関連特許(Patent)

なし.