課題番号 :F-20-TU-0035

利用形態 :機器利用

支援課題名(日本語) :情報環境(インフォスフィア)調和型 自己組織化ヘテロ集積システムの開発

Research Title (English) : Research and Development of 3D LSI

利用者名(日本語) : <u>福島誉史</u>, マリアッパン・ムルゲサン, 金野成秀, 森聖晴 Username (English) : <u>T. Fukushima</u>, M. Murugesan, H. Konno, K. Mori

所属名(日本語) :東北大学 未来科学技術共同研究センター

Affliation (English) : Tohoku University, New Industry Creation Hatchery Center

キーワード/Keyword :成膜・膜堆積, TSV, 3D-LSI

## 1. 概要(Summary)

汎用的なスパッタ装置を用い、特殊合金をバリア層に 用いて三次元積層チップで利用する TSV の電気的特性 の向上を検討した。これにより、次世代の積層型 AI チップ作製の技術基盤を構築する。

## 2. 実験(Experimental)

【利用した主な装置】 芝浦スパッタ装置

## 【実験方法】

アスペクト比 5 以上の Si 深穴に  $SiO_2$ を成膜し、特殊合金でバリア層とCu シード層を形成し、電解めっきでCu を埋め込み、埋込特性の評価とデイジーチェーン配線を作製した。電気的な特性は四端子測定により行った。

#### 3. 結果と考察(Results and Discussion)

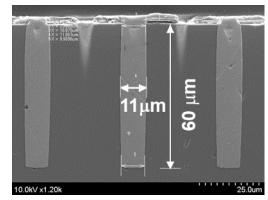

一般的に、Si 深溝に対し、汎用的なスパッタ装置を用いてコンフォーマルで連続的なバリア層、シード層の形成は難しいとされているが、RF Power (300 W)、真空度、ガス流量、ターゲットとサンプルの配置を最適化し、直径10 μm、深さ60 μm、アスペクト比5以上のSi 深穴まで電解 Cu めっき膜を充填することに成功した(Fig. 1)。イオナイズド型でロングスロー方式のスパッタ装置を用いずに、底部、底部側壁の被覆率を5%ほどに向上できた。それによって、電流密度0.3 dA/cm²の硫酸銅Cu めっき(室温)を用いて、シームやボイド無くCuをSi 深溝に充填することができた。ビアラスト三次元集積化方式を採用し、この材料とスパッタ方式を用いて形成したバリア層、Cu シード層を用いて高アスペクト比 TSV の形成を試みた。ウエハ全面内の均一性は高く、ウエハ中央、及びエッジでも同様に Cu を埋め込むことに成功している。また、良好な

## 電気特性も得られた。

Fig. 1 SEM cross-section of Cu-TSV with a special alloy barrier layer formed with a non-ionized / short-through general PVD tool.

# 4. その他・特記事項(Others)

なし。

#### 5. 論文·学会発表(Publication/Presentation)

M. Murugesan, K. Mori1, M. Koyanagi, and T. Fukushima, "A TSV-last Approach for 3D-IC Integration and Packaging using a Platable Barrier-cum-Protective W Alloy Layer", accepted in the 71th IEEE Electronic Components and Technology Conference (ECTC) 2021.

### 6. 関連特許(Patent)

なし。