課題番号 : F-20-TT-0016

利用形態 :共同研究

利用課題名(日本語) :インプラント型デバイスのための最小スペース微細配線技術

Program Title (English) : Sidewall patterning for minimum space wiring in implant-type device

利用者名(日本語) : <u>太田淳</u> Username (English) : <u>Jun Ohta</u>

所属名(日本語) : 奈良先端科学技術大学院大学

Affiliation (English) : Nara Institute of Science and Technology

キーワード/Keyword:リソグラフィ・露光・描画装置、立体配線、最小スペース

### 1. 概要(Summary)

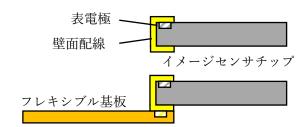

埋込み型バイオデバイスを用いて、生体の運動解析を目指した研究が盛んである。例えば、活動中の脳に密着して測定するイメージセンサである。チップ内は非常に微細なパターンからなるが、チップ外は直径が数十から数百μm の金やアルミ線を用いたワイヤボンディングによって配線されている。ワイヤとシールド材の空間的な膨らみは、センサ面と生体組織を離して像を不鮮明にし、生体組織を圧迫してしまう。埋め込み型バイオデバイスは、生体組織と一緒に機能することが重要で、悪影響を与えてはならない。問題解決には、チップ側面を立体配線に利用して、使用する空間を最小にすることが有効である。Fig.1 に最小スペース微細配線の模式図を示す。チップ壁面を介して、表から裏面をつなげる配線パターンを用意できれば、フリップチップ実装にてフレキシブル基板と接続でき、イメージセンサ面が一番上となって生体組織を撮像できる。

センサチップ壁面への応用を目指すが、センサチップは高価なため、まず同じサイズ、同じ電極パターンを転写した Si 基板を試作して試作に利用することとした。単独チップではなく、1 次元のアレイ状に製作することで、一度に多数のチップで検証実験ができる。

### 2. 実験(Experimental)

## 【利用した主な装置】

マスクレス露光装置、Deep Reactive Ion Etching 装置 (Bosch プロセス)、デジタルマイクロスコープ群など

#### 【実験方法】

センサチップと同程度の厚み 300μm を持つ 4" Si 基板に、センサチップと同じパターンを転写した。Si 基板を約 1.5μm だけエッチングし、チップを強酸等で洗浄してもパターンは残るようにした。

# 3. 結果と考察(Results and Discussion)

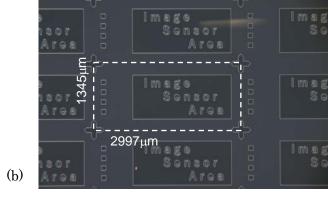

Fig.2 (a)は製作した Si 基板である。2 次元アレイであ

Fig.1 Minimum space wiring. (a) Chip with wall wiring. (b) Connection to flexible substrate through wall wiring.

Fig.2 (a) Si wafer with electrode patterns. (b) Magnified sensor chip unit in array.

る。Fig.2(b) は 拡 大 図 で あ る。チップ 個 片 は  $2997x1345\mu m^2$ である。左側の 4 つの正方形が電極である。この基板を1次元アレイの短冊状にカットして実験に利用する。

## 4. その他・特記事項(Others)

- ・共同研究者:佐々木実(豊田工業大学 教授)

- 5. 論文・学会発表(Publication/Presentation) なし。

- 6. 関連特許(Patent) なし。