課題番号 :F-20-GA-0034

利用形態 :機器利用

利用課題名(日本語) : 教育用シリコントランジスタの作製及び集積化に関する研究

Program Title (English) : Study on Device Fabrication and Integration Process for the Silicon Transistor as

an Educational Device

利用者名(日本語) :長岡史郎

Username (English) : S. Nagaoka

所属名(日本語) :香川高等専門学校 電子システム工学科

Affiliation (English) : Dept. of Electronic Systems Engineering, National Institute of Technology, Kagawa College

キーワード/Keyword :接合、MOS、p-n 接合、デバイスプロセス、集積回路

### 1. 概要(Summary)

半導体デバイス黎明期のゲルマニウムを使った半導体デバイスの研究開発の取り組みをシリコンで再現し、追体験することで、研究開発におけるアイデアの作り方、考え方を学び、材料としてのシリコンの可能性を考察することで、独創性を養うことを目的とした教育用デバイスプロセスの開発に取り組んでいる。デバイスは、ソースとドレインとなる領域における不純物の選択的拡散の実現、ゲート絶縁層の作製と電極作製で実現される。絶縁層はシリコンの熱酸化膜、CVD等による窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)膜が用いられている。Si<sub>3</sub>N<sub>4</sub> 薄膜をスパッタ法で作製し、それを応用した nMOS FET を考案、実際に作製することができた。

#### 2. 実験(Experimental)

## 【利用した主な装置】

デュアルイオンビームスパッタ装置 (ハシノテック社製, 10W-IBS)

触針式表面形状測定器(ULVAC 社製、Dektak8)

# 【実験方法】

基板は、4 インチのシリコン(Si) 基板( $\langle 100 \rangle$ 、約 1-2 $\Omega$ ・cm)を 2 cm 角に切り出して利用した。Si $_3$ N $_4$  薄膜の作製には、イオンビームスパッタ装置と、純度 4N の窒化シリコン(Si $_3$ N $_4$ )の焼結ターゲットを用いた。Si $_3$ N $_4$  薄膜の膜厚は、ゲート酸化膜として用いるため 60 nm と 100 nm に設定した。膜厚分布が 2 cm 以内で 3%以内となるように基板を配置した。膜厚は、成膜前にサンプル基板とテープにより作製した薄膜段差を用いて成膜後触針式の装置で実測し、成膜速度と分布を評価し、成膜条件を決定、その条件で成膜を行った。

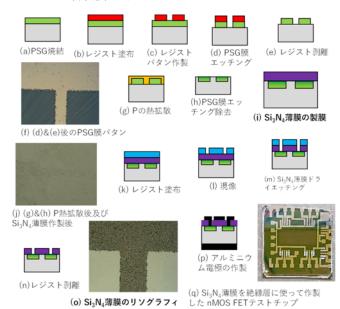

Fig. 1 A photograph of the  $Si_3N_4$  thin film prepared by the dual ion beam sputtering

#### 3. 結果と考察(Results and Discussion)

Fig. 1 に成膜した Si<sub>3</sub>N<sub>4</sub> 薄膜とそれを用いたデバイスプロセスを示す。フォトリソグラフィはマスクパタンの位置合わせを必要としない方法を考案した。この特徴を生かし、最初にソースとドレインとなる n 領域を実現し、その後、絶縁層、電極などを作製した。Fig. 1(j)に示すとおり、Si<sub>3</sub>N<sub>4</sub> 薄膜がきれいに成膜できている事がわかる。Fig. 1 (o)はドライエッチング後の Si<sub>3</sub>N<sub>4</sub> 薄膜の写真である。ピンホールなどなく、加工できていることがわかる。Fig. 1(q)に Si<sub>3</sub>N<sub>4</sub> 薄膜を絶縁層に応用した nMOS FET を示す。電極に用いたアルミニウム薄膜のエッチング残りはあるが、nMOS FETを含む TEG チップを作製できた。教育用のデバイスとして有用であると期待される。今後素子特性等の評価を実施する。

- 4. その他・特記事項(Others) なし。

- 5. 論文・学会発表 (Publication/Presentation) なし。

- 6. 関連特許(Patent) なし。