| 課題番号                   | :F-20-AT-0143                                                                  |

|------------------------|--------------------------------------------------------------------------------|

| 利用形態                   | :機器利用                                                                          |

| 利用課題名(日本語)             | :pMOS デバイスのゲート酸化物としての酸化ケイ素                                                     |

| Program Title(English) | :Silicon oxide as gate oxide for pMOS devices                                  |

| 利用者名(日本語)              | :ロザック ミカエル                                                                     |

| Username(English)      | : <u>Mickael Lozac'h</u>                                                       |

| 所属名(日本語)               | :一般社団法人ミニマルファブ推進機構、産業技術総合研究所                                                   |

| Affiliation(English)   | :Minimal Fab Promoting Organization, National institute of advanced industrial |

|                        | science and technology (AIST)                                                  |

| キーワード/Keyword          | :形状・形態観察、分析、Gate oxide, SiOx, Si-O stretching mode                             |

## <u>1. 概要(Summary)</u>

Our research focus on the silicon-oxide (Si-O) stretching mode from FTIR to assess the quality of p-channel metal-oxide-semiconductor field effect transistor (p-MOSFET), also called pMOS. We are investigating the possibility to link the density of interface states ( $D_{it}$ ), between the gate oxide (SiO<sub>x</sub>) and the Si wafer, and the Si-O stretching mode. Here, the optical properties of the silicon oxide are monitored by Fourier Transform Infra-Red (FTIR) and coupled with the gate oxide process, the chemical cleaning process prior to the gate oxide deposition, and  $D_{it}$  measured on pMOS devices.

## <u>2. 実験(Experimental)</u>

【利用した主な装置】顕微フーリエ変換赤外分光装置 (FT-IR) 【 実 験 方 法 】The pMOS devices are fabricated by Minimal Fab: an advanced, costeffective, semiconductor fab where the area of the required cleanroom level is minimized to the surrounding of the silicon wafers (with a diameter of 12.5 mm), encapsulated in a shuttle during the full fabrication process. Then, the D<sub>it</sub> estimated from C-V analysis and the Si-O stretching mode are systematically monitored.

## 3. 結果と考察(Results and Discussion)

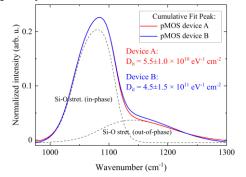

For two pMOS devices A and B realized in a similar process, the  $D_{it}$  is estimated by C-V measurements at  $5.5\pm1.0 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$  and  $4.5\pm1.5 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$ , respectively. The Si-O stretching mode, located at the wavenumbers from 1000 cm<sup>-1</sup> to 1250 cm<sup>-1</sup>, and its deconvolution, is shown in Fig. 1. The devices are well deconvoluted into two peaks noted in-phase and out-of-phase (Fig.

1). Interestingly, the integrated area of the Si-O stretching out-of-phase is slightly larger for the pMOS device B that also presents a larger D<sub>it</sub>. This could be attributed to some impurities present at the interface and/or some slight damages due to the fabrication process after the high temperature annealing (1150 °C for 1h) for the gate oxide. The nature of such impurity and its concentration or the possible damages still under process are investigation. Besides, the stoichiometry x of the silicon oxide  $(SiO_x)$  can also be determined with the position of the Si-O stretching mode in-phase. We estimate a similar stoichiometry about 1.91±0.01 and 1.92±0.01 for the pMOS devices A and B, respectively. Thus, coupling the FTIR analysis with D<sub>it</sub> could be useful for the determination of the Gate oxide quality and its interface with the Si wafer.

Fig. 1 FTIR Si-O stretching mode for two different pMOS devices A and B with respective D<sub>it</sub>.

- <u>4. その他・特記事項(Others)</u>なし。

- <u>5. 論文・学会発表(Publication/Presentation)</u>

- M. Lozac'h, S. Khumpuang, and S. Hara, JSAP 68<sup>th</sup> Spring Meeting (2021).

- <u>6. 関連特許(Patent)</u>なし。