課題番号 : F-20-AT-0073

利用形態 :技術代行

利用課題名(日本語) :GaAs 基板への高アスペクト比のスルービアの形成

Program Title (English) : The formation of high aspect ratio through vias into GaAs substrates

利用者名(日本語) :樋口貴文, <u>宇佐美浩之</u> Username (English) :T. Higuchi, <u>H. Usami</u>

所属名(日本語) : 富士ゼロックス 株式会社 Affiliation (English) : Fuji Xerox Co..Ltd.

キーワード/Keyword : 膜加工・エッチング、GaAs、Resin、Deep Etching

### 1. 概要(Summary)

光通信に使われる VCSEL(Vertical Cavity Surface Emitting LASER)の高密度実装のため、スルービア形成による電極取り出し構造を検討している。 GaAs 基板は、Si 基板と比べウェハが脆弱であるため、より厚い基板膜厚が求められ、そのためにはより深いビアを形成する必要がある。

19 年度から産業技術総合研究所(AIST)の設備を使った、高スループットかつ高アスペクト比(A/R)なビア加工条件を検討し高アスペクト比(A/R)加工条件を決定した。今年度は、80 μm 径(電極パッドサイズ相当)、深さ 100 μm 以上の垂直形状ビアを持つ VCSEL デバイス構造形成を行った。

#### 2. 実験(Experimental)

## 【利用した主な装置】

化合物半導体エッチング装置(ICP-RIE) コンタクトマスクアライナー[MJB4]

#### 【実験方法】

高アスペクト比エッチング用の厚膜レジストを形成した3 インチ GaAs 基板を4インチ Si 基板に真空グリスおよび カプトンテープで固定したのち、化合物半導体エッチング 装置でエッチングを行った。

#### 3. 結果と考察(Results and Discussion)

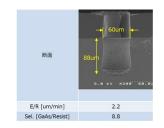

GaAs ドライエッチング条件は、昨年度に条件確認を行った垂直形状が得られる低バイアスエッチング条件を使用した(Fig. 1)。

Fig. 1 Through hole vias after GaAs etching.

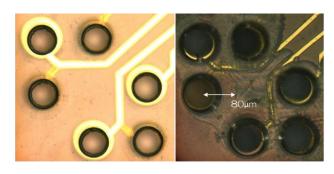

Fig. 2(a)は GaAs エッチング前の状態、Fig. 2(b)は GaAs エッチング後の状態である。

Fig. 2(a) Through vias pattern before GaAs etching.

Fig. 2(b) Through vias pattern after GaAs etching.

100 μm の深堀をしたところ、基板の温度上昇などにより層間膜(樹脂膜)の密着性が低下している。

今後、層間膜形成条件の見直し、ICP エッチングによる ダメージ(熱)を低減する条件などを引き続き探索していく。

# 4. その他・特記事項(Others)

なし。

# 5. 論文・学会発表 (Publication/Presentation) なし。

# 6. 関連特許(Patent)

なし。