課題番号 :F-19-GA-0034

利用形態 :機器利用

利用課題名(日本語) :マイクロ合金トランジスタ作製用デバイスプロセスに関する研究

Program Title (English) : Study on device process for fabrication of Silicon Micro-Alloy Bipolar Transistor

利用者名(日本語) :<u>長岡史郎</u> Username (English) :<u>S. Nagaoka</u>

所属名(日本語) :香川高等専門学校 電子システム工学科

Affiliation (English) : Dept. of Electronic Systems Engineering, National Institute of Technology, Kagawa College

キーワード/Keyword :形状・形態観察、分析、バイポーラトランジスタ、Dektak 8

## 1. 概要(Summary)

半導体デバイス黎明期の半導体デバイスの性能改善の考えをシリコンで再現するため、シリコンの異方性エッチングを用いたバイポーラトランジスタの設計製作評価を検討している。デバイスは、異方性エッチングでトランジスタ領域を決定し、熱拡散でエミッタとコレクタの不純物濃度を制御しバイポーラトランジスタとする。ここでは異方性エッチングマスクとなる窒化シリコン薄膜をスパッタ法で作製した。その結果、膜厚が約 100nm と約 200nm の窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)薄膜が作製できた。

## 2. 実験(Experimental)

#### 【利用した主な装置】

- (1) デュアルイオンビームスパッタ装置 (ハシノテック社製、10W-IBS)

- (2) 触針式表面形状測定器(ULVAC 社製、Dektak8)

#### 【実験方法】

基板は、4 インチのシリコン(Si)両面基板(〈100〉、約  $12\Omega \cdot cm$ )を用いた。Si $_3N_4$  薄膜の作製には、イオンビームスパッタ装置と、純度 4N の窒化シリコン(Si $_3N_4$ )の焼結ターゲットを用いた。Si $_3N_4$  薄膜の膜厚は、異方性エッチング時における  $Si_3N_4$  薄膜と結晶シリコンのエッチング速度の選択比が 1000 以上と非常に大きいため、薄くても大きな問題は発生しないと考えられるが、今回製作したSi $_3N_4$  薄膜を別の目的に応用することも考慮しているため、100nm と 200nm に設定した。作製した基板は 2cm 角に切り出して利用する。そこで、膜厚分布として 2cm 以内で 3% 以内を目標に設定した。膜厚は成膜前にサンプル基板とテープにより作製した薄膜段差を用いて成膜後触針式の装置で実測し、成膜速度と分布を評価し、成膜条件を決定、その条件で成膜を行った。

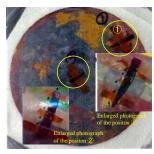

Fig. 1 A photograph of the evaluation method of the in-plane distribution of the thickness of  $Si_3N_4$  thin film

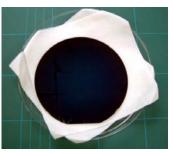

Fig. 2 A photograph of Si<sub>3</sub>N<sub>4</sub> thin film on the both side of 4 inch silicon substrate

### 3. 結果と考察 (Results and Discussion)

Fig. 1 に成膜した Si<sub>3</sub>N<sub>4</sub> 薄膜の膜厚と膜厚の面内分布を求めたサンプルを示す。測定の結果、中心から約20mmの範囲で3%以内の分布を実現できた。これは、4インチの基板全面でほぼ満足していることを確認した。

Fig. 2 に 4 インチの基板に成膜した結果を示す。まず、 片面に成膜した後、真空室から取り出し、裏面に同様に 成膜した。きれいな分布で成膜できていることが分かる。こ れにより、目的の基板を作製できた。

#### 4. その他・特記事項(Others)

なし。

# 5. 論文·学会発表(Publication/Presentation)

なし。

#### 6. 関連特許(Patent)

なし。