課題番号 :F-18-IT-0033

利用形態 :技術代行

利用課題名(日本語) :シリコン細線プラズモン光導波路に関する研究

Program Title (English) : Research on Plasmonic Si Wire Waveguides

利用者名(日本語) :塩道溪,前田拓海,宮内智弘,清水大雅

Username (English) : K. Shiomichi, T. Maeda, T. Miyauchi and H. Shimizu

所属名(日本語) :東京農工大学 工学府 電気電子工学専攻

Affiliation (English) : Tokyo University of Agriculture and Technology

キーワード/Keyword:シリコンフォトニクス、表面プラズモン、光アイソレータ、ダイシング、切削、研磨、接合

#### 1. 概要(Summary)

プラズモン導波路とは金属と誘電体の界面に表面 プラズモンポラリトン(Surface Plasmon Polariton: SPP)を励起することで光を伝搬させる素子であり、セ ンサやアイソレータへの応用が期待されている。金属 部に Fe などの強磁性金属を用いることで、磁気光学 効果により非相反損失や移相を実現でき、Si 導波路光 アイソレータへ応用することができる[1]。ジュール損 失の小さい Au を組み合わせることで伝搬損失を低減 した、非相反移相器を方向性結合器へ搭載し、伝搬方 向によって結合度が異なること(非相反結合)を利用し た TM モード光アイソレータを報告してきた[2]。し かし、これらは Si 細線導波路上への金属薄膜の選択 的形成等作製の難しさから実現には至っていない。そ こで本研究では、斜め電子線蒸着により Fe/Au 積層 構造を Si 導波路側壁に製膜し、一次元の光閉じ込め を考慮した計算(等価屈折率法)により TE モードで動 作するアイソレータの構造を検討してきた[3]。

本研究では、センサやアイソレータへの応用に向けた、Si 細線導波路の片側側壁に Fe/Au 積層構造を製膜した TE モードで動作するプラズモン導波路の作製を目的とする。一次元の光閉じ込めを考慮した設計により得られた構造にて、FDTD 法により二次元の光閉じ込めを考慮したシミュレーションを行い、設計の妥当性について考察する。さらに素子の作製プロセスを確立し、モードコンバータを搭載した Si 細線導波路を試作し、伝搬損失と結合損失を評価した。

## 2. 実験(Experimental)

【利用した主な装置】

ダイシングソー

【実験方法】

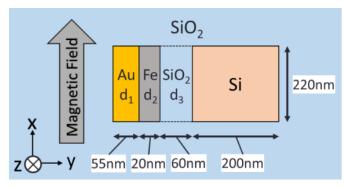

片側側壁に Fe / Au 積層構造を製膜した Si 細線導波路の構造を Fig.1 に示す。Si 導波路の幅は多モードの励振を避けるため 200 nm とし、入力光は波長 1550 nm の TE モードとした。Si コア層の厚さは 220 nm である。Si コア層と金属層の間には  $SiO_2$  バッファ層 (層厚  $d_0$ )がもたらす磁気光学効果と伝搬損失を調整した。さらに Fe による伝搬損失を低減させるために Fe 層の外側に Au 層(層厚  $d_0$ )を設けた。各層厚を可変とし、性能指数を最大化する 導波路構造を目指した。

Si 細線導波路の側壁に成膜する三層(Au / Fe / SiO2) の膜厚を最適化した。Au、Fe、SiO2層の膜厚をそれぞれd =10~100 nm、d =10~50 nm、d = 5~700 nm の範囲内を 5 nm 刻みで変化させ、各膜厚の組み合わせから実効屈折率を前進光 / 後退光に対して求めた。伝搬長が 1, 2, 3…µm となる条件で、それぞれ前進光と後退光に対する実効屈折率の実部の差Re[ $\Delta n_{eff}$ ]が最大となる膜厚の組み合わせを求めた[2]。伝搬長を 2  $\mu$ m に設定したとき、Re[ $\Delta n_{eff}$ ]を最大化する各層の膜厚の組み合わせは(d, d, d3) = (55, 20, 60) nm となり、このとき Re[ $\Delta n_{eff}$ ] = 0.0059 となった。

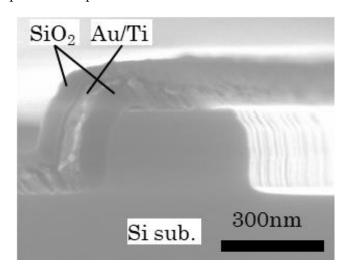

電子線描画とエッチングにより幅 400 nm の導波路を形成した Si 基板を用いて、斜め蒸着を用いた Fig.1 の構造を作製するためのプロセスを検証した。まず Fe を用いず Au のみを製膜した。Au と SiO2 は密着性が悪いため、間に Ti を挿入した。金属層を保護するため、外側に SiO2を製膜した。  $(SiO_2/Ti/Au/SiO_2)$ をそれぞれ(100 nm/3 nm/100 nm/50 nm)の厚さで順に角度 85 度の斜め蒸着により製膜し、Si をエッチングした際のレジストマスクを剥離液によって溶かすリフトオフ法により側壁への選択的製膜を試みた。また、SOI 基板上に上記プラズモン導波路構造を試作すべく、

導波路の幅を 400 nm から 200 nm に変換するモード コンバータを作製した。作製した導波路をダイシング ソーにより切断・へき開した。

Fig.1 A schematic cross-sectional image of the Si wire waveguide with Au/Fe for designing plasmonic optical isolators

Fig.2 A cross sectional scanning microscope image of the fabricated Si rib structure with SiO2 / Au / Ti layers by electron-beam evaporation with substrate tilted.

## 3. 結果と考察(Results and Discussion)

得られた試料の断面 SEM 像を Fig.3 に示す。Si 導波路の片側側壁にのみ金属層がはがれることなく製膜できることを確認した。またモードコンバータ 1 個あたりの結合損失は TE, TM モードともに 1.8 dBとなった。2.で設計したプラズモン導波路の伝搬損失と比較して小さく、第一次試作としては良好な結合損失が得られた。今後、Si 細線導波路とプラズモン導波路の集積を目指す。

# <u>4. その他・特記事項(Others)</u>

#### 参考文献

[1] T. Kaihara et al., Opt. Express 25 730 (2017).

[2] H. Shimizu et al., Jpn. J. Appl. Phys., 57(4S): 04FN07 (2018).

## 本研究に関わる競争的資金

科学研究費補助金 基盤研究(B) 課題番号 16H04346 「強磁性金属表面プラズモンを利用する革新的光アイソレータの開発」研究代表者: 清水大雅

## 5. 論文·学会発表(Publication/Presentation)

- (1)清水大雅「スピン磁性フォトニクスデバイスーシリコンフォトニクスと光アイソレータ・メモリー」電子情報通信学会 第28回シリコンフォトニクス研究会 東京工業大学大岡山キャンパス 平成30年7月25日.

- (2) 塩道渓, 下平貴大, 清水大雅「強磁性金属・貴金属 積層 Si プラズモン導波路におけるTEモード磁気光学 性能指数の解析」2018 年応用物理学会秋季学術講 演会 18a-212A-3, 平成 30 年 9 月 18 日.

#### 6. 関連特許(Patent)

なし。