課題番号 :F-17-TU-0059

利用形態:機器利用

利用課題名(日本語) :金属膜の多層構造形成

Program Title (English) : Deposition of multi-layered metal

利用者名(日本語) :村上俊也

Username (English): T. Murakami所属名(日本語): 株式会社東芝

Affiliation (English) : Toshiba Corporation

キーワード/Keyword : 成膜・膜堆積、スパッタ、多層積層、金属、薄膜

#### 1. 概要(Summary)

半導体デバイスには、半導体材料、絶縁体材料、金属 材料等の種々の材料が使用されている。金属は配線など に使用されているが、求められる性能は電気伝導性に加 えて、不純物拡散防止能や機械的強度、加工精度等の 多岐にわたる。素子の特性は主に膜自身の物性による部 分が多いが、素子の微細化に伴い薄膜界面の状態がデ バイス性能へ強く影響してくる。たとえば、成膜中や成膜 後の熱履歴、デバイス使用時に印加される電圧などにより、 原子拡散がおこったり欠陥が導入されたりする。その結果、 デバイス性能の劣化につながり、性能の保証ができないと いう問題が発生する可能性がある。そのため、薄膜界面 の状態をコントロールする手法や、ナノスケールでの薄膜 界面の評価手法の確立が必要不可欠である。このような 背景から、本研究では、薄膜界面の理解を深めるために、 異種金属材料の界面を作製することとした。今回は、金属 材料としてアンチモン(Sb)、タングステン(W)を選択し、こ れらの多層薄膜を成膜したときの膜の密着性等を確認し た。

## 2. 実験(Experimental)

## 【利用した主な装置】

電子ビーム蒸着装置

芝浦スパッタ装置

Dektak 段差計

#### 【実験方法】

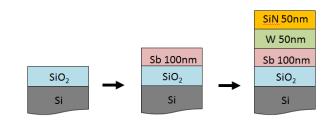

酸化膜付シリコン基板(Si/SiO<sub>2</sub>)に Sb を電子ビーム蒸着法により 100nm 程度成膜し、その後スパッタリングにより W と窒化シリコン膜(SiN)をそれぞれ 50nm 程度積層した。成膜後の試料構造は、Si 基板/SiO<sub>2</sub>/Sb/W/SiN である。 W と SiN の成膜は同一装置で実施し、真空一貫にて連続的に成膜した。成膜イメージを Figure1 に示した。比較用に Si/SiO<sub>2</sub> 基板に W および SiN を成膜した

(Si 基板/SiO<sub>2</sub>/W/SiN)。SiN 層は、W の酸化を防止する ためのキャップ層としての機能を有す。

Figure 1 Deposition of Sb, and W and SiN on Si/SiO<sub>2</sub> substrate

#### 3. 結果と考察(Results and Discussion)

Sb上にWを成膜したSi基板/SiO2/Sb/W/SiNの試料では、成膜後目視で白濁が確認でき、膜剥がれが発生していることが分かった。一方、Si基板/SiO2/W/SiNの試料では膜剥がれの無い均一な膜が形成した。このことからSb/W界面は膜の密着性が悪いことが予想される。原因としてはWの内部応力が高いことと、Sb表面の酸化によることが考えらえる。今後、正常な異種金属の界面を得るために、Wの成膜条件の最適化や、逆スパッタ等によるSb表面の酸化膜除去プロセスの導入等が必要であると考える。

Table 1 Results

| 基板構造                            | 膜剥がれ |

|---------------------------------|------|

| Si基板/SiO <sub>2</sub> /Sb/W/SiN | あり   |

| Si基板/SiO <sub>2</sub> /W/SiN    | なし   |

## 4. その他・特記事項(Others)

なし

# 5. 論文・学会発表 (Publication/Presentation)

# 6. 関連特許(Patent)

なし