課題番号 :F-17-TU-0013

利用形態:機器利用

利用課題名(日本語) : 半導体ナノ構造の作製

Program Title (English) : Fabrication of semiconductor nanostructures

利用者名(日本語):遊佐剛1),松浦雅広1)

Username (English) : <u>G. Yusa</u><sup>1)</sup>, M. Matsuura<sup>1)</sup>

所属名(日本語) :1) 東北大学大学院理学研究科

Affiliation (English) :1) Department of Physics, Tohoku University

キーワード/Keyword :リソグラフィ・露光・描画装置, GaAs 半導体, 電子線描画

#### 1. 概要(Summary)

GaAs 半導体試料の上に、微細な金属ゲート電極を設置するため、電子線描画装置を用いた。特に電子線のドーズ量の最適化を行い、GaAs/AlGaAs ヘテロ接合を有する GaAs 基板に表面ゲート電極を設置した。

## 2. 実験(Experimental)

## 【利用した主な装置】

EB 描画装置(エリオニクス・ELS-G125S)

# 【実験方法】

レジストを塗布した GaAs 基板に電子線描画した。

#### 3. 結果と考察 (Results and Discussion)

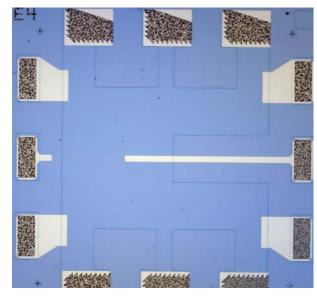

電子線描画装置を用いてレジストにパターニングし、Ti、Au からなる金属ゲートを蒸着した試料の顕微鏡写真を Fig. 1 と 2 に示す。ドーズ量を最適化したことにより、段切れのない幅 1  $\mu$  m の細線金属ゲート電極を設置することができた。

## 4. その他・特記事項(Others)

・GaAs 半導体基板は物質・材料研究機構、野田武司氏、間野高明氏から提供された。

## 5. 論文·学会発表(Publication/Presentation)

- (1) 松浦雅広, 他, 日本物理学会秋季大会(ポスター)

- (2) Masahiro Matsuura, Takaaki Mano, Takeshi Noda, Naokazu Shibata, Masahiro Hotta, and Go Yusa, Appl. Phys. Lett. 112, 063104 (2018)

- (3) Masahiro Matsuura, Kick-off Symposium for World Leading Research Centers (ポスター)

## 6. 関連特許(Patent)

なし。

Fig. 1 Optical microsocpe image of a device. Evapolated gold metals function as metal gate electroldes.

Fig. 2 The enlarged image near the gate electrodes processed by e-beam writer.