課題番号 :F-16-NM-0044

利用形態 :機器利用

利用課題名(日本語) :洗浄プロセスの電気特性に及ぼす影響

Program Title (English) : Impact of electrical property on gate pre-cleaning process

利用者名(日本語) :白神 健太郎

Username (English) : <u>Kentaro Shiraga</u>

所属名(日本語) :東京エレクトロン株式会社 Affiliation (English) :Tokyo Electron Limited

## 1. 概要(Summary)

洗浄工程における要求・制約は、素子の微細化に伴い増加している。そこで本報では、いくつかの洗浄プロセスをゲート前洗浄に適用し、ゲートスタックの電気特性に及ぼす影響を調査した。

## 2. 実験(Experimental)

# 【利用した主な装置】

原子層堆積装置

## 【実験方法】

15mm 角の Si 基板に対して、5 種類の洗浄プロセス (A, B, C, D, E)を各々行い、その後、原子層堆積装置 にて TMA と  $H_2O$  を用いて  $Al_2O_3$  を 120  $^{\circ}$  で 8nm 堆積 した。続いて、PVD 装置にて TiN を 30nm 成膜し、ゲートパターンを形成し、フォーミングガス中で 400  $^{\circ}$  の熱処 理を行い、nMOS キャパシターを作成した。

#### 3. 結果と考察 (Results and Discussion)

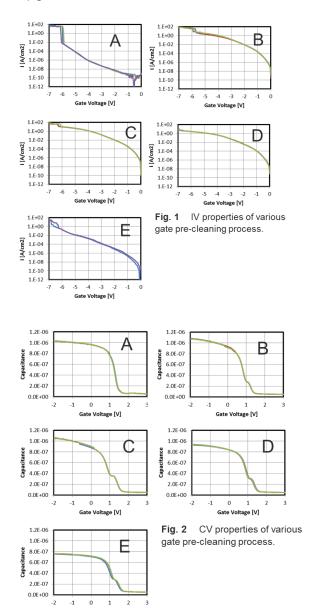

Figure 1 にゲートリーク電流特性を示す。ゲートリーク特性は、前工程の洗浄プロセスにより大きく異なることが判明した。中でも最も良好な特性を示したものは洗浄プロセス A であった。おそらく、洗浄プロセスによる Si 表面状態の差異が Al2O3 成膜初期ステージに影響していることを示唆しており、Si 表面の終端構造などに関しては、今後調査を進めるものとする。

続いて、Fig.2 に CV 特性を示す。洗浄プロセス B-E にかけて CV カーブにハンプが認められ、界面特性が劣化していることが判明した。

以上、ゲート前洗浄プロセスがゲートスタックのリーク特性および Si 界面特性に影響することが明らかとなった。

# 4. その他・特記事項(Others)

本課題を実施するに当たり、NIMS 微細加工 PF の大

里啓孝様にご協力いただきました。ここに感謝の意を表します。

# <u>5. 論文・学会発表 (Publication/Presentation)</u>なし。

#### 6. 関連特許(Patent)

なし。