課題番号 :F-15-WS-0036

利用形態 :技術代行

利用課題名(日本語) :銅の埋め込みシリコン貫通電極の作製

Program Title (English) : Fabrication of through silicon via filling by copper

利用者名(日本語) :<u>藤井 剛 1)</u>

Username (English) :<u>G. Fujii</u>1)

所属名(日本語) :1) 国立研究開発法人 産業技術総合研究所 ナノエレクトロニクス研究部門 Affiliation (English) :1) National Institute of Advanced Industrial Science and Technology

## 1. 概要(Summary)

近年、超伝導デジタル回路、超伝導量子コンピュータ、X線センサなどの超伝導デバイスにおいて、回路の大規模化が進んでおり、それに伴うチップサイズの拡大が問題となっている。現在、8層の配線層を積層することで、チップサイズを縮小することに成功しているが、高い歩留まりを維持しつつ、さらに積層数を向上させることは非常に困難である。そこで、半導体デバイスで既に採用されているSi貫通電極(TSV)を形成したチップを積層し、TSVで積層したチップ上のデバイス同士を接続する実装方法を超伝導デバイスにも応用可能であるかを検証するため、TSVの作製を行っている。今回、3インチシリコンウェハに作製した貫通穴に、早稲田大学微細加工プラットフォームのメッキ装置を利用し、銅の埋め込みを行った。

## 2. 実験(Experimental)

【利用した主な装置】

- めっき装置

- CMP 研磨システム

## 【実験方法】

初めに、産業技術総合研究所(AIST)超伝導アナログデジタルデバイス開発施設(CRAVITY)及び物質・材料研究機構(NIMS)微細加工プラットフォームの装置を利用し、厚さ 400 μm の 3 インチシリコンウェハに貫通穴を作製した。貫通穴は、直径 70 μm の穴が 150 μm 間隔で400×400 個形成されている。さらに、貫通穴以外のウェハ表面は、電解メッキ用のシード層として、Ti(10 nm)/Au(300 nm)膜が成膜されている。次に、早稲田大学微細加工プラットフォームのめっき装置を用いて、電解めっきにより、貫通穴に銅の埋め込みを行った。その後、電極となる貫通穴以外のウェハ表面全体に形成されてしまった銅を除去するため、化学機械研磨(CMP)装置を用いて、ウェハ表面の銅の除去を行った。

## 3. 結果と考察 (Results and Discussion)

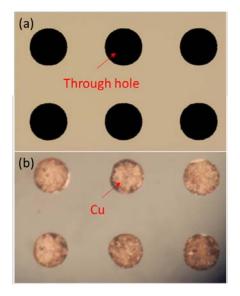

貫通穴と銅が埋め込まれた貫通穴の顕微鏡画像を Fig. 1 に示す。直径 70 μm の貫通穴に銅を隙間なく埋め込むことが出来ている。一方で、貫通穴以外の部分は銅が除去出来ている。次に、触針式膜厚計を用いて、銅が埋め込まれた貫通穴の表面形状を測定した。銅が埋め込まれた部分が約 1 μm 凹んだ構造となっており、表面近傍まで銅が充填出来ている。今後、電子顕微鏡を用いて、へき開したウェハの断面観察を行い、ボイドの有無などを評価する予定である。

Fig. 1 Microscope images of (a) through holes and (b) through holes filling by copper.

4. その他・特記事項(Others) 競争的資金名:科研費 若手研究(B)

5. 論文・学会発表 (Publication/Presentation)なし

6. 関連特許(Patent)

なし