課題番号 :F-15-UT-0094

利用形態 :共同研究

利用課題名(日本語) :三次元積層 IC チップへの内装を目指したシリコンマイクロ流体素子の作製と封止

Program Title (English) : Integration of Microfluidic Deices to Silicon for 3-D stacked IC chip

利用者名(日本語):大場隆之1)、藤本興治1,2)、良尊弘幸1,3)

Username (English) : <u>Takayuki Ohba</u><sup>1)</sup>, Koji Fujimoto<sup>1,2)</sup>, Hiroyuki Ryoson<sup>1,3)</sup>

所属名(日本語) : 1)東京工業大学 WOW アライアンス, 2)大日本印刷株式会社, 3)デクセリアルズ株式会社

Affiliation (English) : 1)WOW Alliance, Tokyo Institute of Technology, 2)Dai Nippon Printing,

3)Dexerials Corp.

### 1. 概要(Summary)

次世代の集積回路においては、PLL(位相同期ループ) 回路のような高速動作を行う回路において局所的に高い温度が発生することによって、チップ全体の性能が制限されるという課題が指摘されている。チップ中に存在する高温部分のことをホットスポットと呼び、効率的な冷却デバイスを集積化することによってホットスポットを解消しようとする研究が盛んにおこなわれている。代表者らのグループでは、流体を循環する冷却デバイスに注目し[1]、長年にわたり研究を行っている。研究の進展に伴い、電子回路とMEMS デバイスの集積の必要性が生じてきたため、東京大学と新たに共同研究を開始した。研究一年目として、シリコン基板上に金属電極付のマイクロ流路を形成し、外部から観察するために透明な封止剤で封止する、電極付マイクロ流路素子を作製するプロセス技術の習得を目標として研究を行った。

### 2. 実験 (Experimental)

# 【利用した主な装置】

4 インチ高真空 EB 蒸着装置、高速電子線描画装置、 光リソグラフィ装置

#### 【実験方法】

シリコンウエーハ上に酸化膜を8インチスパッタリング装置によって製膜したのち、ステルスダイサーによって切断し、IC(集積回路)基板を模した2cm角のチップに切り出した。チップ上に電極金属を4インチ高真空EB蒸着装置によって製膜し、高速電子線描画装置ならびに自動現像装置によって作製したフォトマスクを用い、光リソグラフィ装置によってパターンを転写し、塩素系ICPエッチング装置によって電極パターンを形成した。さらに光リソグラフィ装置によって流路パターンを形成し、高速シリコン深掘りエッチング装置によって流路パターンを形成し、高速シリコン深掘りエッチング装置によって流路パターンを形成し、高速シリコン深掘りエッチング装置によって流路パターンを形成し、高速シリコン深掘りエッチング装置によって流路パターンを形成し、高速シリコン深加りエッチング装置によって流路が多点に高密度プラズマスパッタ装置によって絶縁膜材料を成膜した。

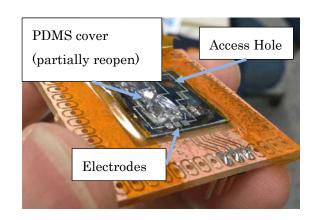

Fig. 1 Photograph of Fabricated Device

各工程でチップの洗浄にはドラフトチャンバーを用い、電子顕微鏡(SEM)で構造を観察確認した。作製したチップと、別途スピンコーターで作製したポリジメチルシロキサン(PDMS)膜とを接合し封止した。

## 3. 結果と考察(Results and Discussion)

上記実験により作製した流体チップを Fig. 1 に示す。 流路の封止技術の選択が最も困難な課題で、接着強度 の不足や接合部のμm級のギャップからの流体の漏れといった問題が生じた。そのため数多くの失敗を繰り返した。 最終的に、PDMS と酸化膜との接合が最も高い強度が 取れることが分かった。今後は確立したデバイス作製技 術を用いて、新たな MEMS 構造によるホットスポット冷却 手法の実験を行う予定である。

# 4. その他・特記事項(Others)

共同研究者:東京大学工学系 岡本有貴 三田吉郎 参考文献:[1]Y.S.Kim *et. al,* 2011 Symposium on VLSI Technology Digest of Technical Papers, pp. 144-145

5. 論文・学会発表 (Publication/Presentation)

#### 6. 関連特許(Patent)

なし