課題番号 :F-15-UT-0064

利用形態:機器利用

利用課題名(日本語) :Si 基板の実装

Program Title (English) : Mounting of a Si substrate

利用者名(日本語) : <u>東野 二郎</u>, 熊谷 光恭, 大和田 聡二, 喜來 省吾 Username (English) : <u>J. Higashino</u>, M. Kumagai, S. Owada, S. Kirai

所属名(日本語) :スタンレー電気株式会社

Affiliation (English) : Stanley Electric, Co. Ltd.

## 1. 概要(Summary)

サブマウント上に複数個の Si チップを一定の間隔で実装し、その間隔を制御する。

## 2. 実験(Experimental)

## 【利用した主な装置】

精密フリップチップボンダー

## 【実験方法】

サブマウント上にはんだペーストを塗布し、精密フリップ チップボンダーを用いて Si チップを一定間隔で配置した。 その後、精密フリップチップボンダーに付随の加熱機構を 用いて、はんだ共晶を行い、Si チップの実装を行った。

評価項目としては共晶前後の Si チップの間隔を測定する。

## 3. 結果と考察(Results and Discussion)

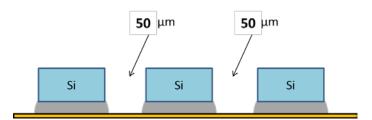

サブマウント上にはんだペーストを用いて Si チップを  $50~\mu m$  間隔で 5~ 本実装を行った。(Fig.1)

実装装置の加熱機構を用いてはんだ共晶を行い、共 晶前後の Si チップ間隔を測定したところ、所望の Si 間隔 を得ることができた。

Fig. 1:Implementation of chip

同条件にて5個のSiチップを実装したサンプルを5個 用意し、全て同じ条件で加熱共晶を行い、Si チップのば

## らつきを調査した。

共晶前の Si 間隔を基準とし、その変化量を調査したと ころ、結果として、3  $\sigma$ で $\pm$ 20  $\mu$ m の範囲に入ることが分 かった。

## <u>4. その他・特記事項(Others)</u>

なし。

# 5. 論文·学会発表(Publication/Presentation)

なし。

#### 6. 関連特許(Patent)

なし。