課題番号 :F-15-IT-0007

利用形態 :技術代行

利用課題名(日本語)

Program Title (English) : Making test samples for optical assembly technology demonstration

利用者名(日本語) :

Username (English) :<u>J. Cai<sup>1)</sup></u>

所属名(日本語) :1) 華為技術日本株式会社

## 1. 概要(Summary)

Great efforts have been contributed to silicon photonics in academia during the past decade. Due to the promising low-power consumption and low-cost solution, various products based on silicon photonic technology have been announced in recent years. Assembly of the optical components is one of the key issues to achieve a complete photonic product. In this work, we prepared some trench structures for optical components assembly test, aiming at the demonstration of optical components assembly technology.

## 2. 実験(Experimental)

## 【利用した主な装置】

触針式段差計

### 【実験方法】

Silicon chips containing trench/groove structures were fabricated and then the dimensions, especially the depth of the trench were characterized by surface profiler.

# 3. 結果と考察(Results and Discussion)

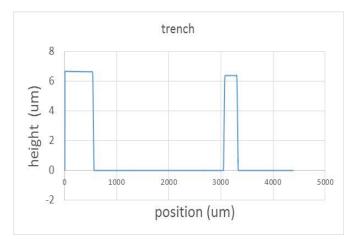

For optical components assembling, the precision of fabrication is critical in case of using passive alignment method. For example, in case of a laser to a silicon waveguide coupling, an error of one micrometer can give rise to an over 30% reduction of coupling efficiency. In this work we prepared wet/dry etched trenches and employed the surface profiler to check the dimensions of the fabricated structure. Figure 1 plots the typical image of the surface tomography, showing a measured 6.5um height of the trench. Compared with a designed 7um height, 0.5um deviation of etching depth is observed. Other results also predict a less than one

micron deviation by comparing the designed values and the fabricated ones. It should be noted that the precision of the depth could be possibly realized by carefully adjusting the recipe of the etching process. The results mentioned above indicate that the sub-micron accuracy of etching process can be achieved, indicating the possibility of passive alignment using similar structure.

Fig. 1 Surface profile of a fabricated trench on Si chip

#### 4. その他・特記事項(Others)

We thank Professor Nobuhiko Nishiyama for the fabrication of the test samples.

# <u>5. 論文•学会発表(Publication/Presentation)</u>

なし。

## 6. 関連特許(Patent)

なし。