課題番号 :F-15-FA-0059

利用形態 :機器利用

利用課題名(日本語) :ダイシング加工による SiC チップ試料作製

Program Title (English) : Fabrication of SiC chip samples by singulate process

利用者名(日本語) :<u>石地耕太朗</u> Username (English) :<u>K. Ishiji</u>

所属名(日本語) :九州シンクロトロン光研究センター

Affiliation (English) : Kyushu synchrotron light research center

# 1. 概要(Summary)

近年、次世代半導体 SiC の研究開発が盛んである。ショットキーバリアダイオードや MOS など様々なデバイスの実用が始まっているが、十分な電気特性を発揮しているとは言い難い。積層欠陥やキラー転位や結晶歪みなどが電気特性を低下させているためである[1, 2]。それらの欠陥は結晶成長中に発生することもあるが、デバイス処理中にも発生する[3, 4]。しかし、どの段階でどのような欠陥が導入するかはあまり分かっていないうえ、処理条件にも大きく左右される。そこで、標準的なダイオード処理過程中の欠陥構造変化を調査することにした。ダイオード化にはイオン注入と高温アニールが欠かせないが、各工程で表面歪み形状や X 線トポグラフィーを用いて欠陥構造評価を行うことを計画している。

#### 2. 実験(Experimental)

## 【利用した主な装置】

ダイシング加工マシン

## 【実験方法】

今回、未処理状態の3インチ径SiCウェハーを手に入れた。ダイオード化処理を行うが、処理条件を変えるので、チップ状試料を30個ほど用意する必要がある。そこで、ダイシングマシンで10mm²のチップ状に加工した。

## 3. 結果と考察(Results and Discussion)

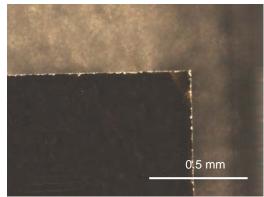

3 インチウェハーから 32 個のチップ試料を切り出した。 Fig.1 に切断したチップ試料の写真を示す。切断後、ウェハーの切り出し位置が分かるようにケースに格納した。 Fig.2 にチップ試料の端を拡大した顕微鏡写真を示す。 ギザギザや欠けなどなく、きれいな切断面であった。今後、 1 個 1 個のチップ試料に条件を変えてダイオード化処理 を行う予定である。

Fig.1 SiC-Chip(10×10mm)

Fig.2 Edge of SiC Chip

## 4. その他・特記事項(Others)

#### 参考文献

- [1] K. Fukuda, et al., Mater. Sci. Forum 645, 655 (2010).

- [2] H. Fujiwara, et al., Appl. Phys. Lett. 100, 242102 (2012).

- [3] K. Ishiji, S. Kawado, Y. Hirai, and S. Nagamachi, J. Appl. Phys. 113, 194505 (2013).

- [4] K. Ishiji, S. Kawado, Y. Hirai, and S. Nagamachi, Mater. Sci. Forum 778, 449 (2014).

- 5. 論文・学会発表 (Publication/Presentation) なし。

# 6. 関連特許(Patent)

なし。