課題番号 : F-15-AT-0129

利用形態 : 技術代行

利用課題名(日本語) : 次世代エレクトロニクスデバイ スの試作・評価 (PJ3)

Program Title (English) : Experimental production and evaluation of a next generation electronics device

(project 3)

利用者名(日本語) :<u>佐々木恭</u>、廣岡哲也 Username (English) :<u>Y.Sasaki</u>、T. Hirooka

所属名(日本語) :ティーイーアイソリューションズ株式会社

Affiliation (English) : tei Solutions Co., Ltd.

## 1. 概要(Summary)

次世代エレクトロニクスのデバイス開発を目的としたシリコンウエハへの加工評価を行うため、産業技術総合研究所ナノプロセシング施設(NPF)の設備を利用した。

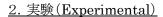

本報告では、Fig. 1 に示すような、極細のAu電極の作製及び出来栄えを確認するための抵抗測定について、記述する。

## 【利用した主な装置】

真空蒸着装置

ナノプローバー(技術代行)

### 【実験方法】

- (1) 他施設で作製した 4 インチパターン付ウエハに、真空 蒸着装置をもちいて、Au/Cr 膜を成膜した。

- (2) そのウエハをリフトオフし、Fig. 1 のような Au 電極を 作製した。

- (3) ナノプローバーで測定できるように、5 mm 角ぐらいに、 サンプルを小さくし、I-V 測定を行った。

#### 3. 結果と考察(Results and Discussion)

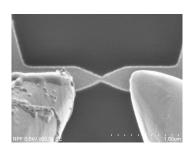

- (1) 抵抗@0.1V n=50 は、以下のようになった。平均値:147Q、最大:386Q、最小 127QI-V 波形を Fig. 2 に示す。

- (2)また、測定時に静電破壊起因と思われる破壊痕があるサンプルがあった。微細な Au 電極のサンプルを扱う時は、除電などをして慎重にサンプルを扱う必要がある。

- (3) 今後、Au のナノギャップ電極を作製し、本ナノプローバーで抵抗を測定して、出来栄えを確認していく予定である。

Fig. 1 The measurement pattern by Nano Probe.

Fig. 2 I-V Characteristic.

4. その他・特記事項(Others) なし。

5. 論文・学会発表 (Publication/Presentation) なし。

# 6. 関連特許(Patent)

なし。