課題番号 :F-15-AT-0066

利用形態 :技術代行

利用課題名(日本語) :原子層堆積装置を用いた TiN ゲート電極の成膜

Program Title (English) : TiN deposition for MOS gate electrode using atomic layer deposition

利用者名(日本語) :近藤佳幸 Username (English) :Y. Kondo

所属名(日本語) :東京エレクトロン株式会社 Affiliation (English) :Tokyo Electron Ltd.

## 1. 概要(Summary)

FINFET などの三次元構造を有する MOSFET 作製を目的として原子層堆積装置を利用し、TiNゲート電極を成膜した。本課題では平面素子での試験評価まで行った。素子の評価は MOSCAP による C-V 測定と Planar 型 MOSFET による  $I_D-V_G$  測定を行った。

## 2. 実験(Experimental)

InGaAs/InP の薄片基板上に  $Al_2O_3$  を 10 nm 堆積した試料を用意した。この試料に Table 1 に示す条件で TiNの成膜を行った。#2 は Tiソースを供給する前にも 30 秒間  $N_2$ プラズマを照射し、酸化膜表面の窒化処理を行う条件である。これらの試料を用いて MOSCAP を作製して C-V 測定を行った。そして結果が最適だった条件の試料で MOSFET を作製した。

Table 1: Conditions for TiN deposition.

|                      | #1  | #2  | #3  |

|----------------------|-----|-----|-----|

| Temperature [°C]     | 200 | 200 | 200 |

| ICP Power [W]        | 200 | 200 | 300 |

| Nitridation prior to | No  | Yes | No  |

| Ti source supply     |     |     |     |

| Cycle                | 200 | 200 | 200 |

## 3. 結果と考察(Results and Discussion)

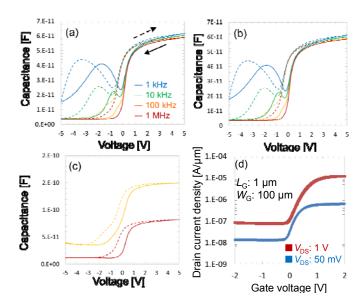

Fig. 1(a)-(c)は  $1 \, \text{kHz} - 1 \, \text{MHz}$  間の C-V 特性である。 # $1 \, \text{と#}2$  に差異は見られなかった。しかし#3 では高周波側の周波数分散が大きかったため低周波側の測定を省略した。#1,2 における蓄積側での周波数分散は  $2 \sim 4$  %で、従来使用してきた Ta 電極と大きな差は見られなかった。 これより# $1 \, \text{を MOSFET}$  作製用の条件に設定した。またコンダクタンス法で調べた結果、Mid gap 付近の界面準位密度は  $2 \times 10^{12} \, \text{eV}^{-1} \text{cm}^{-2}$  とMOSFET を作製するために十分な値を確認することができた。

Fig. 1: MOSCAP C-V and MOSFET ID-VG performances in each conditions (a) C-V for #1 (b) C-V for #2, (c) C-V for #3, (d) ID-VG for #1.

条件#1 の試料を用いて作製した N 型 MOSFET の  $I_0$ -  $V_0$  特性が Fig. 1(d)である。On/off 比 2 桁程度の FET 変調特性を見ることができた。しかしゲート電極経由のリークが大きいため、TiN のエッチング条件やソース/ドレインの形成条件の見直しを検討する必要があると言える。上記課題を解決した後、三次元構造素子の作製をしていきたいと計画している。

## 4. その他・特記事項(Others)

- ・本研究は東京大学微細構造解析 PF 及び NIMS 微細加工 PF の支援を併用した。

- ・共同研究者: 大場大輔、軍司勲男 (東京エレクトロン)

# 5. 論文・学会発表 (Publication/Presentation)なし。

#### 6. 関連特許(Patent)

なし。