課題番号 :F-14-YA-0027

利用形態 :技術代行

利用課題名(日本語) :半導体微細領域の電気特性

Program Title (English) : Study of micro-scale electrical characterization of semiconductors

利用者名(日本語) :<u>阿部 友紀</u> Username (English) :<u>T. Abe</u>

所属名(日本語) :鳥取大学 大学院工学研究科

Affiliation (English) :Graduate School of Engineering, Tottori University.

### 1. 概要 <u>(Summary)</u>

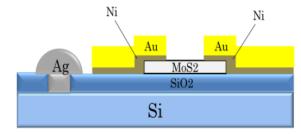

近年、ナノエレクトロニクスデバイス材料として、グラフェンをはじめとした二次元層状半導体の研究が盛んに行われている。しかし、グラフェンはバンドギャップをもっておらず、トランジスタなどのアプリケーションに適さない。そこで、同じく二次元構造であり、単層で 1.8 eV のバンドギャップをもつ半導体である MoS<sub>2</sub> に着目した。今回、MoS<sub>2</sub>をスコッチテープ法により剥離して SiO<sub>2</sub>/Si ウエハに転写した。その上にフォトリソグラフィーを用いて Cr/Au ソース、ドレイン電極をパターニングして、ボトムゲート型の TFT を作製した。

#### 2. 実験 (Experimental)

・利用した装置:マスク描画装置(香川大学)

山口大学で設計を行った後、香川大学のマスク描画 装置を用いてマスクを作製した。基板は 300 nm の SiO<sub>2</sub> 膜を表面に形成した Si 基板を用い、UV オゾン 処理にて親水処理をし、HMDS (ヘキサメチルジシラザン)をスピンコートで塗布してベーキングを行った。 基板への転写はスコッチテープで結晶を何度も劈開し、スコッチテープを基板に貼り付けて圧力を加えることにより行った。

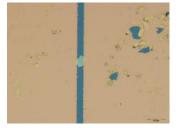

作製したマスクを用いたフォトリソグラフィーと 真空蒸着で Cr/Au ソース、ドレイン電極を形成し、基 板をゲートとしたボトムゲート型 TFT を作製した。 (Fig. 1, 2)

### 3. 結果と考察(Results and Discussion)

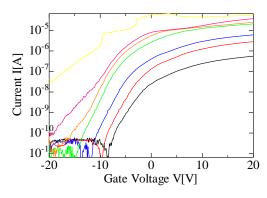

作製した素子はゲート電圧によりドレイ電流が変調されるトランジスタとしての動作特性を示した。オフ電流はゲート電圧-10 V以下で $10^{-10} \text{ A}$ 以下となり、on/off 比は $10^6$  (Fig. 3)、電解移動度は $0.32 \text{ cm}^2$ /Vs であった。

これは十分な値ではなく、原因として MoS2の膜厚

が 15 nm と単層 0.65 nm に比べて厚いためであると 考えられる。

## <u>4. その他・特記事項 (Others)</u>

香川大学(支援番号: F-14-GA-0025)、山口大学(F-14-YA-0027)と協力して支援頂いた。

5. 論文・学会発表 (Publication/Presentation) なし

# 6. 関連特許 (Patent)

なし

Fig. 1 Structure of TFT

Fig. 2 Microphotograph of TFT

Fig. 3 Current-voltage characteristics of TFT