課題番号 : F-14-RO-0026

利用形態 :共同研究

利用課題名(日本語) :DNA/Si メモリートランジスタの基板作製・評価(DNAトランジスタ作製)

Program Title (English): Fabrication and Evaluation of DNA Memory Transistor-Fabrication of DNA

FET-

利用者名(日本語) :松尾直人,中村昇平

Username (English) : N. Matsuo, S. Nakamura

所属名(日本語) :兵庫県立大学大学院工学研究科

Affiliation (English) : Graduate School of Engineering, University of Hyogo

# 1. 概要(Summary)

従来の CMOS (Complementary Metal-Oxide Semiconductor)回路の作製はトップダウン手法で行われる事から微細化が進むに従い、作製が困難になり、ULSI(ultra-large scale IC)の集積度が 1.5 倍で約 2 倍というムーアの法則(Moore's Law)がもはや成立しない段階に到達している。CMOS のゲート長が 22nnm 世代においては、Si に代わる材料の出現が期待されている 1)。DNA(DeoxyriboNucleic Acid)は電流を流す性質を持ち、さらに自己組織化によってナノ構造体を形成する 2)事から、カーボンナノチューブ 3)やグラフェン 4)同様に、Beyond CMOS の材料といての性質があり、無機半導体と同様にゲート電圧を変化させることで、トランジスタ特性を示すことが知られている 5)。本研究室では、DNA チャネル/SiO2/Si(ゲート)構造におけるキャリア挙動について調査した。

## 2. 実験(Experimental)

・利用した主な装置:酸化炉,マスクレス露光装置,エッチング装置(RIE SiO2用),真空蒸着装置

#### • 実験方法

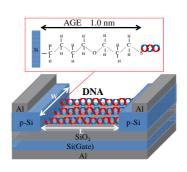

Fig.1 には作製した DNA メモリートランジスタの模式図を示す。p-Si 活性層膜厚 50 nmを目標として酸化炉にて酸化とエッチングを行い、マスクレス露光装置 (100 mJ/cm²)とCDE装置 (CF4:  $O_2$ =100:100 sccm, 0.4 Torr, 40 s)を用いて p-Si アイランドの形成を行った。アイランド形成後、真空蒸着装置を用いて Al 蒸着、ウェイトエッチング ( $H_3PO_3$ = 500,  $HNO_3$ = 33,  $CH_3COOH$ = 100,  $H_2O$ = 33) により電極形成を行った。

# 3. 結果と考察 (Results and Discussion)

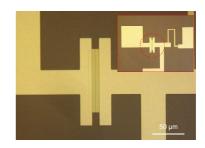

Fig.2 は Al 電極形成後に確認したインバータ回路(チャンネル長 120 nm)顕微鏡写真である。これにより p-Si アイランドの形成および Al 電極の蒸着を正常に行ったと

Fig.1 Schematic configuration of DNA Memory Transistor

Fig.2 Photomicrograph image (channel length 120nm).

考えられる。

## 4. その他・特記事項(Others)

共同研究者:横山新教授,福山正隆教授,佐藤旦研究員[参考文献]

- 1) R. Martel *et al.*, IEEE IEDM Tech.Dig., (2001),159-162.

- 2) K. Nagashio *et al.*, IEEE IEDM Tech. Dig. (2009) 565-568.

- 3) International Technology Roadmap for Semiconductors (ITRS) (2010) Edition.

- 4) D. Porath et al., : Nature 403 (2000) 635.

- 5) B. Xu et al., : Nano Lett. 4 (2004) 1108.

- 5. 論文·学会発表(Publication/Presentation)

- S. Maeno *et al.*, "Study of Charge Retention Mechanism for DNA Memory FET", IEICE Electronics Express, Vol.11, No.5, pp.1-6, 2014.

- 6. 関連特許(Patent) なし。