課題番号 :F-14-NM-0124

利用形態 :技術代行

利用課題名(日本語) :イオン注入を施した酸化物半導体トランジスタ試作のためのプロセス開発

Program Title (English) : A Fabrication Process for An Oxide Semiconductor Transistor

利用者名(日本語) :<u>清水 貴思</u> Username (English) :<u>T. Shimizu</u>

所属名(日本語) :產業技術総合研究所

Affiliation (English) : National Institute of Advanced Industrial Science and Technology

## 1. 概要(Summary)

イオン注入を行った IGZO (InGaZnO<sub>x</sub>) 系酸化物半導体を微細トランジスタへ加工するためのプロセス技術開発を行うため、酸化物半導体のハードマスクとして用いる酸化物薄膜のナノメートルスケールの微細加工の可能性を調べた。マスクレス露光によってラインアンドスペースに加工したフォトレジスト上に ALD (Atomic Layer Deposition) 法で酸化物薄膜を堆積し、ALD 前後の側壁の荒さを測定することによって、ハードマスクとしての可能性を調べた。

### 2. 実験 (Experimental)

# 【利用した主な装置】

- ・ダイシングソー DAD322

- ・プラズマ CVD 装置 PD-220NL

- ・マスクレス露光装置 DL-1000

- ・原子層堆積装置 SUNALE™ R-100B

- ・酸化膜ドライエッチング装置 MUC-21 RV-APS-SE

- ・多目的ドライエッチング装置 RIE-200NL

### 【実験方法】

プラズマ CVD (Chemical Vapor Deposition) 装置によって 100~150nm の膜厚の SiO2を Si ウェハ上に堆積し、ダイシングソーによって 10mm 角程度のチップに加工した。その後、マスクレス露光装置によって、間隔 2μm 以下のフォトレジストのラインアンドスペースパターンを作成した。酸化膜ドライエッチング装置を用いて、下地の SiO2を加工するとともに、フォトレジストのラインアンドスペースパターンをわずかにエッチングし、レジスト形状を整えた。その後、ALD 法を用いてフォトレジストで作成した間隔2μm 以下のラインアンドスペースパターン上に酸化物薄膜を 30~50nm 堆積した。多目的ドライエッチング装置を用いて RIE (Reactive Ion Etching) プロセスを施したのち、AFM (Atomic Force Microscopy) を用いて薄膜の側壁の荒さを評価した。

## 3. 結果と考察 (Results and Discussion)

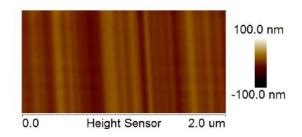

Fig.1 は、酸化膜ドライエッチング装置を用いて形状を整えた後のフォトレジストパターンの側壁荒さを示す AFM 像である。R<sub>max</sub> が 67.1nm、R<sub>ms</sub> が 9.24nm であった。

Fig.1. AFM image of a side wall of a pfotoresist pattern

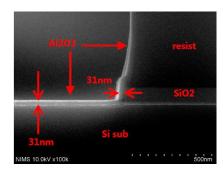

このようなフォトレジストパターン上に ALD 法で Al<sub>2</sub>O<sub>3</sub> 薄膜を 31nm 堆積した試料の断面 SEM (Secondary Electron Microscopy) 像を Fig.2 に示す。

Fig. 2. A cross-sectional SEM image of a photoresist pattern covered with  $Al_2O_3$  film by ALD.

下地 Si、フォトレジスト上ともに均一な薄膜が堆積でき、側壁表面荒さは  $R_{max}$  が 176nm、 $R_{ms}$  が 25.6nm であった。 4. その他・特記事項(Others)

5. 論文・学会発表 (Publication/Presentation)

6. 関連特許 (Patent)

なし

なし