課題番号 :F-14-BA-14 利用形態 :技術代行

利用課題名(日本語) :グラフェンの合成と電気特性評価

Program Title (English) :Synthesis of graphene and evaluation of their electrical properties.

利用者名(日本語) :桑島 知也,秋山蒼太郎、猪狩智彦、檜山卓希

Username (English) : Tomoya Kuwajima, Sotaro Akiyama, Tomohiko Igari, Takaki Hiyama

所属名(日本語) : 筑波大学大学院数理物質科学研究科電子物理工学専攻

Affiliation (English) : University of Tsukuba

#### 1. 概要(Summary)

グラフェンは高い電子移動度、優れた光透過率を有することから、次世代高速トランジスタや透明電極など様々な分野での応用が期待されている。これらの応用では、層数を制御した結晶性の良いグラフェンの大面積合成が重要な課題となっている。現在最も有力な大面積グラフェン合成手法は Cu 基板上への CVD(Chemical Vapor Deposition)合成であるが、Cu 基板から絶縁基板上へのグラフェン転写プロセスが必要となる。我々の研究グループでは、Ga 蒸気を触媒として用いた CVD によって絶縁基板上に大面積のグラフェンを直接合成する手法を見出し、その電気特性の評価を行った。

### 2. 実験(Experimental)

石英管加熱炉内に Ga のリザーバーと熱酸化膜付き Si 基板を配置し、常圧下で炉管内にメタンとアルゴンガスを 導入し 1050 度で加熱すると、石英基板表面は Ga 蒸気と メタンガスの混合雰囲気に暴露され、表面全体にグラフェンが合成される。合成したグラフェンの電気特性評価のために、マスクレス露光装置、電子ビーム蒸着装置を用いた リフトオフプロセスによりグラフェン FET (Field Effect Transistor)を作成した。

## 3. 結果と考察 (Results and Discussion)

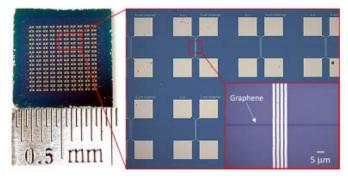

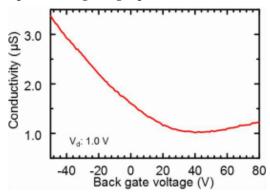

図1に作成したグラフェン FET の光学顕微鏡写真を示す。 1 cm 角基板にフォトリソグラフィー・蒸着・リフトオフプロセスを用いて、80 個のグラフェン FET を作成した。図2に作成したグラフェン FET のバックゲート電圧に対する導電率依存性を示す。グラフェンに特異的な Dirac 点が観測された。また Dirac 点は 40 V 付近に存在し、合成したグラフェンはp型を示すことが分かった。これはフォトリソグラフィーで用いたレジスト残渣の影響が考えられる。 導電率の傾きから求めたホール移動度は 3.8 cm²/Vs であった。

Fig.1 Optical image of graphene FETs

Fig.2 Conductivity-back gate voltage curve of graphene FET

#### 4. その他・特記事項(Others)

本研究は JSPS 科研費 23246063 および 26107506 の 助成を受けたものです。

# 5. 論文・学会発表 (Publication/Presentation)なし。

#### 6. 関連特許(Patent)

なし。