課題番号 :F-14-AT-0049

利用形態 :機器利用

利用課題名(日本語) : 次世代エレクトロニクスデバイスの試作・評価 PJ001

Program Title (English) : Process and evaluation of the next generation electronics device PJ001

利用者名(日本語) : <u>鈴木 慎一</u> Username (English) : <u>S. SUZUKI</u>

所属名(日本語) :ティーイーアイソリューションズ株式会社

Affiliation (English) : tei SOLUTIONS Co., Ltd.

## 1. 概要(Summary)

素子の電気特性測定評価のため,層間絶縁膜  $SiO_2$ と Ta/Al 積層膜を、RF スパッタリング装置を使用して形成した。

#### 2. 実験(Experimental)

- (1)シリコン酸化膜 層間絶縁膜形成

- ・基板 3インチシリコン基板

- ・装置 CFS-4EP-LL スパッタ装置

- ・ターゲット材料 SiO2

- •温度 常温

- ・スパッタ前クリーニング 無し

- ·条件 0.5Pa Ar 9.5+ O2 0.5sccm RF 400W 20min

- ·設計膜厚 SiO<sub>2</sub> 300 ±30nm

#### (2) Ta /Al 積層膜形成

- ・基板 3インチシリコン基板

- ・装置 CFS-4EP-LL スパッタ装置

- ・ターゲット材料 Ta および Al

- ・温度 常温

- ・スパッタ前クリーニング 無し

- ・条件 (Ta/Al は連続成膜)

Ta  $0.3\mathrm{Pa}\,\mathrm{Ar}$   $10\mathrm{sccm}\;\mathrm{RF}\;200\mathrm{W}\;30\mathrm{sec}$

Al 0.5Pa Ar 10sccm RF 200W 28min

·設計膜厚 Ta 5 ±0.5nm、Al 400 ±40nm

## 3. 結果と考察(Results and Discussion)

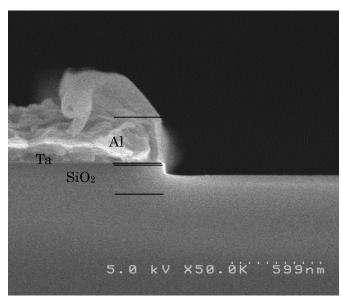

Fig.1 に上記仕様で作製した基板のAl およびTa 積層 膜ドライエッチング後の断面形状をしめす。

SiO<sub>2</sub>、Ta および Al がそれぞれ 300、5、400 nm 程度 に膜厚形成されている。

Ta および Al のカバレジも良好であり、下地 Si/SiO2間 および SiO2/Ta/Al 間の界面において剥離等は発生して

いない。

Fig.1 The cross section SEM image after the Al dry etching process.

## 4. その他・特記事項(Others)

なし。

# <u>5. 論文·学会発表(Publication/Presentation)</u>

なし。

## 6. 関連特許(Patent)

なし。