課題番号 :F-13-UT-0135

利用形態 :共同研究

利用課題名(日本語) : CMOS-MEMS 集積型新規センサに向けた CMOS ポストプロセスの実施及び評価

Program Title (English) : Study of CMOS Post-Process toward CMOS-MEMS Integrated Future Sensors

利用者名(日本語) : 関口亮太, 尾内敏彦

Username (English) : <u>Ryota Sekiguchi</u>, Toshihiko Ouchi 所属名(日本語) :キヤノン株式会社・総合 R&D 本部

Affiliation (English) : Canon Inc.

### 1. 概要(Summary)

東京大学 VDEC がナノプラットで提供する CMOS マルチチップウエーハと、キヤノンによる高周波用センサ素子とを融合した、新規センサを作製する。融合の問題点として挙がった「CMOS 後工程において回路が受ける熱の影響」に関して、検討を進めた。とくに半導体後工程上の熱履歴に関して、想定する熱履歴を経た CMOS デバイス・回路の作製から特性評価まで検討を進めた。

### 2. 実験 (Experimental)

キヤノン株式会社では、次世代の高周波センサ向けの新規素子の研究を行っている。これまで自社内の開発で、基幹部品である単体の検出素子プロセスが固まってきたので、システムとしての性能検証の段階として、素子の近傍で情報処理(増幅、レベル変換、アドレッシング等)を行うために、大規模集積回路(VLSI)と集積化したいと考えている。

具体的には、トランジスタ回路を作製した6インチシリコンウエーハを受け取り、社内ならびに東京大学 微細加工拠点でポストプロセス加工を行い、テストデバイスを作製する。

共同研究1年目は、融合・集積することが物理層レベルで可能かどうか熱履歴の観点で検証する。そこで、受け取ったウエーハに検出素子プロセスで用いる熱ストレスを印加し、CMOS及びトランジスタ回路が正常機能するかを確かめた。手段としては、ポストプロセスTEG(Test Element Group)素子・トランジスタ回路を設計・及び作製し、電気特性を評価した。ポストプロセスTEG素子作製は、東京大学VDECの電子線描画装置・ダイシング装置を用いて、VDEC澤村氏、エリック氏の技術協力を用いて完成した。

## 3. 結果と考察(Results and Discussion)

はじめに、ポストプロセス TEG 素子を設計した。 半導体バルクのシート抵抗を求めるための TLM (Transmittion line method) パターン、半導体一金 属コンタクト抵抗を求めるための Greek-Cross 型 Kelvin パターンを配置、不純物拡散を検査するための p-n 接合素子、MOS 素子ならびに簡単なトランジスタ 回路も設計した。 設計には、VDEC が提供する Cadence 社 IC CAD を用いた。

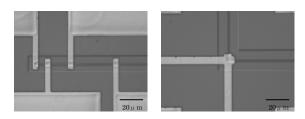

次に、ポストプロセス TEG 素子・トランジスタ回路を作製した。これらを搭載する CMOS マルチチップウエーハには半導体前工程で出荷したものを用意した。ウエーハは、ナノプラットのダイシング装置によってチップに分割し、それぞれのチップには想定するプロセスフローを経た熱ストレスを与えた。こうして疑似的に検出素子を融合したチップに、ナノプラットの電子線描画装置、自社の成膜装置・エッチング装置を用いて、半導体後工程を施した(Fig.1)。

最後に、ポストプロセス TEG 素子・トランジスタ 回路の電気特性評価を行った。熱ストレスを受けた素子と、そうでないものと比べたところ、拡散層抵抗器 は熱ストレス印加による変化がN型、P型ともにみられなかった。各種半導体一金属コンタクト抵抗、N型 拡散層一金属コンタクト、P型拡散層一金属コンタクトのそれぞれについて抵抗の変化を計測し、データを取得した。MOS トランジスタ素子の電流電圧特性及びしきい値電圧を同様に評価したところ、ポストプロセス前後で変化がなく、良好な特性を示した。

## <u>4. その他・特記事項(Others)</u>:

# 共同研究者:

三田吉郎 東京大学大学院工学系研究科 准教授

Fig.1 Fabricated Post-Process Device.

<u>5. 論文・学会発表(Publication/Presentation)</u>:

なし

6. 関連特許 (Patent)

なし