課題番号 :F-13-HK-0003

利用形態 :機器利用

利用課題名(日本語) :原子層堆積装置(SUNALE-R)によるAl<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub>膜の作製

Program Title (English) : Formation of Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> film by atomic layer deposition apparatus (SUNALE-R)

利用者名(日本語) :辻田卓司, 西谷幹彦, 北川雅俊

Username (English) : <u>T. Tsujita</u>, M. Nishitani, M. Kitagawa

所属名(日本語) :大阪大学大学院工学研究科 パナソニック材料デバイス基盤協働研究所

Affiliation (English) : Graduate School of Engineering, Osaka University

## 1. 概要(Summary)

近年、メモリーデバイスやキャパシタへの応用が期待され、高誘電率材料の開発が勢力的に行われている。我々はこれらの研究の中で Wei Li 等により報告された  $Al_2O_3$ 及び  $TiO_2$ の積層膜  $(Al_2O_3/TiO_2$ 膜)を用いた実験に着目した。 1nm よりも薄い  $Al_2O_3$ 及び  $TiO_2$ のサブレイヤーを積層することにより、 $\epsilon$  が 1000 を超えるような巨大誘電率が出現することが報告されている 10。今回は、Wei Li 等の実験結果をトレースし、巨大誘電率出現の実証及びメカニズムを考察することを目的とした。

## 2. 実験 (Experimental)

利用した主な装置の名称:原子層堆積装置(SUNALE-R) 実験方法

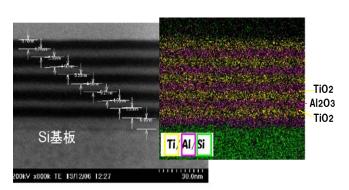

本課題の $Al_2O_3$  /  $TiO_2$  膜を作製する前に、 $Al_2O_3$  及び $TiO_2$  の成膜レート及び、所望の $Al_2O_3$  /  $TiO_2$  膜が得られることの確認を行った。図 1 に膜厚 5nm の $Al_2O_3$  及び $TiO_2$  膜をSi 基板上に計 10 層積層したサンプルの分析結果を示す。

$Al_2O_3$ 及び  $TiO_2$ が 5nm の厚みで制御され、積層できていることが分かる。

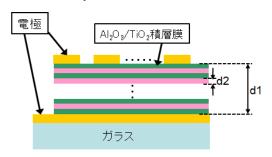

図 2 に、本課題で作製した簡易デバイスの模式図を示す。ガラス - 電極 -  $Al_2O_3$  /  $TiO_2$  膜 - 電極の構成であり、 $Al_2O_3$  /  $TiO_2$  膜の全厚を d1、各サブレイヤー

Fig.1 STEM and EDX images of Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> multilaver on Si substrate

Fig.2 Schematic Diagram for capacitor

の膜厚を d2 ( $Al_2O_3$ 、 $TiO_2$ の膜厚は同じ) とし、d1 を  $50\sim150$ nm、d2 を 3nm 以下として、その組み合わせ を変更した数種類のデバイスを作製し、評価した。

## 3. 結果と考察(Results and Discussion)

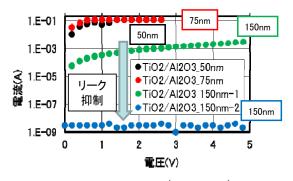

作製した数種類の簡易デバイスのうち、一例として各サブレイヤーの膜厚 d2 を 0.5nm に固定し、全厚 d1 を 50 ~150nm に変化させたときの I-V 特性を図 3 に示す。図 3 に示すように、本課題で作製したサンプルは、すべて低抵抗であり、容量の測定を行うことができなかったため、 $\epsilon$  を見積もることができなかったが、少なくとも、全厚を厚くすることで、電荷リークを抑えられることが分かった。 今後、全厚を厚くした取り組みを進める。

Fig.3 I-V curve (Example)

4. その他・特記事項 (Others)

参考文献

- 1). Wei Li et al, Appl. Phys. Lett. 96, 162907 (2010).

- <u>5. 論文・学会発表(Publication/Presentation)</u>なし

- <u>6. 関連特許(Patent)</u>

なし