課題番号 :F-13-AT-0163

利用形態 :機器利用

利用課題名(日本語) :AFM による相変化膜の電気特性測定用試料作成プロセスの検討(3)

Program Title (English) :Investigation of processing for measuring electric property of phase-change

material by using conductive AFM (3)

利用者名(日本語) :小高 貴浩

Username (English) : Takahiro Odaka

所属名(日本語) :最先端研究開発支援プログラム「グリーン・ナノエレクトロニクスのコア技術開発」

Affiliation (English) :FIRST program "Development of Core Technologies for Green Nanoelectronics"

## 1. 概要(Summary)

相変化メモリ素子は、結晶・アモルファス相転移による 抵抗変化を利用して記録を行うメモリ素子である。本研究 では、サブ 50 nm の微細な電極に AFM でコンタクトしパ ルス電流を印加することにより書換えの測定を行っている が、今回は書換え電力の素子寸法依存性(スケーリング 特性)測定のため、相変化膜上へ電極形成可能なプロセ スを検討した。スケーリング特性測定のためには、相変化 膜表面へのコンタクト面積を規定する必要があるため、相 変化膜上へ成膜した絶縁膜(SiO2)のホール加工を行い、 穴底の面積により素子寸法を規定した。RIE およびリフト オフにより形成した電極と記録膜との導通確認を行うため、 下部電極膜にワイヤボンダーを用いて配線を引出し、導 電AFMにより導通を確認することによりプロセス条件の追 い込みを行った。本プロセスにより相変化膜上に形成した 電極に導電性 AFM でパルス電圧を印加することにより、 書換え動作を測定することが可能となった。

## 2, 実験(Experimental)

#### 利用装置:

電子ビーム描画装置、RIE 装置、スパッタ装置、小型真空蒸着装置、光学顕微鏡、FE-SEM、ワイヤボンダー

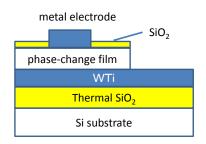

今回作製した構造は Fig. 1 の通りである。熱酸化膜成膜 Si 基板上に、WTi 50 nm を形成後、基板の半面をマスクした基板へスパッタリングにて相変化膜および SiO2膜を形成した。電子ビーム描画装置にて30-150 nm のホールパターンを形成後、RIE にて SiO2をエッチングし相変化膜表面を露出後、電極金属を埋め込みリフトオフにて電極を形成した。素子下部の WTi 膜露出部をワイヤボンダーにて別基板パッドと電気的に接続し電気特性測定用の試料を形成した。

## 3. 結果と考察(Results and Discussion)

$SiO_2$ の RIE 加工は  $O_2$ 添加  $CF_4$ ガスにて行った。RIE のオーバーエッチによる相変化膜の過剰加工を防止するため、RIE 処理時間を数秒間隔で振った加工サンプルを作製し、それぞれについて小型真空蒸着装置にて成膜し形成した電極に AFM プローブで針当てして電圧を印加することにより、相変化膜との導通が取れる RIE 条件を見出した。本素子を用いて、相変化膜へ書換えパルスを印加することにより、相変化に起因する抵抗変化を測定することが可能となった(本報告書では、電気特性の詳細測定結果は割愛する)。

Fig.1 Structure of device for measuring electric property of phase-change film.by using conductive AFM method.

## <u>4. その他・特記事項(Others)</u>

なし。

# 5. 論文・学会発表 (Publication/Presentation)なし。

## 6. 関連特許(Patent)

なし。