課題番号 :F-13-AT-0161

利用形態 :機器利用

利用課題名(日本語) :ミニマルファブ技術の研究開発における分析及び評価

Program Title (English) : Analyses for research and development of Minimal Fab Technology

利用者名(日本語) :居村 史人 Username (English) :F. Imura

所属名(日本語) :ミニマルファブ技術研究組合

Affiliation (English) : Minimal Fab Development Association

## 1. 概要(Summary)

半導体工場の巨大設備投資を回避し、顧客が求める電子デバイスを必要なときに必要なだけ提供するデバイス生産システム(ミニマルファブ構想)の実現に向けて、我々は、クリーンルームを不要とする局所クリーン化ウェハ搬送システム、φ12.5 mm の超小口径ウェハ、それに30cm幅のミニマル装置群の開発を行ってきた。現時点で、前工程プロセスに必要なミニマル装置はほぼプロトタイプが開発されており、ミニマルファブは本当にデバイスができるシステムであることを実証することが、克服すべき大きな課題となってきた。このため、現状のミニマルファブ、ミニマル装置群を用いてMOSFETを作製するためのプロセス構築を行った。このプロセスの構築を行うにあたり、まずは予備実験としてNPF施設を用いてSiハーフインチウェハの基本的なプロセス条件を把握した。

## 2. 実験 (Experimental)

NPF 施設における以下の装置を用いて Si ハーフイン チウェハの各種プロセス(微細加工、成膜、アニールなど)を行った。

- ・反応性イオンエッチング装置(RIE):Si ウェハのドライエッチング

- ·マッフル炉:N2アニール

- ・プラズマ CVD 装置:TEOS 絶縁膜の成膜

- ・プラズマアッシャー:レジスト剥離

- ・高速昇降温炉(RTA):N2アニール

微細加工後の形状観察には以下を用いた。

- •低真空走查電子顕微鏡

- ·高分解能電界放出電子顕微鏡(FE-SEM)

## 3. 結果と考察(Results and Discussion)

MOSFET を作製するためのプロセスを構築し、セミコン会場において実際にMOSFETを作製した。クリーンル

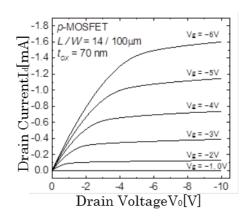

ームを必要とせず、MOSFET 作製工程の一部 30 工程を 約 10 時間で完遂することができた。作製後はすぐにその 場で電気的特性を取得し、トランジスタの典型的なドレイ ン電流・ドレイン電圧の特性を得た。(Fig.1)

Fig. 1  $I_d$ -  $V_d$  characteristics of the p-channel MOSFET.

<u>4. その他・特記事項(Others)</u>なし。

5. 論文・学会発表 (Publication/Presentation) なし。

6. 関連特許 (Patent) なし。