課題番号 : F-13-AT-0125

利用形態 :機器利用

利用課題名(日本語) :ミニマルファブ技術の研究開発における分析および評価

Program Title (English) : Analysis and evaluation for research and development of minimalfab technology

利用者名(日本語) : 浅野 均

Username (English) : Hitoshi Asano

所属名(日本語) :ミニマルファブ技術研究組合

Affiliation (English) : Minimal Fab Development Association

## 1. 概要(Summary)

ミニマルファブでは、ハーフインチウェハを用いて、クリーンルーム環境ではない通常の環境に設置された装置によって半導体プロセスを行う。ミニマル装置でトランジスタを作製するに当たり、まず、MOSFET の基礎構造であるMOSキャパシタを作製し、ミニマル装置で良好なMOS構造が作製できるかを検証する必要がある。その検証において、ハーフインチウェハに対しミニマル装置を用いずに作製したMOSキャパシタが比較対象として必要である。本報告書ではミニマル装置を用いないMOSキャパシタをNPFの小型真空蒸着装置を利用して作製したので、その報告をする。

# 2. 実験 (Experimental)

ピラニア洗浄、RCA 洗浄を行った p型 Si ハーフインチウェハに対し、1100°Cで 1h のドライ酸化を行い、142nmの SiO<sub>2</sub>を製膜した(分光エリプソメトリにて SiO<sub>2</sub> 膜厚を測定)。

その後、NPF 小型真空蒸着装置を用いて、SiO<sub>2</sub> 面に Al を 200nm、Si 面に AuSb を 50nm 蒸着し、MOS キャパシタの電極を作製した。電極のパターニングは蒸着機用に設計したメタルマスクを用いた。作製した MOS キャパシタに対し、C-V 特性の観測を室温で行った。

# 3. 結果と考察(Results and Discussion)

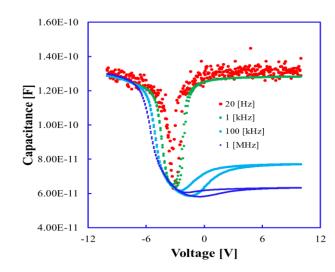

Fig.1 に作製した MOS キャパシタにおいて観測された C-V 特性を示す。C-V 特性は 20, 1k, 100k, 1MHz の周 波数で、 $\pm 10$ V の範囲で観測した。 典型的な p型 MOS キャパシタの低周波 C-V 特性、高周波 C-V 特性が得られて いることがわかる。-10V における容量値から  $SiO_2$  膜厚を 算出すると 143nm となり、分光エリプソメトリで測定した値 とほぼ一致している。

次にフラットバンド電圧の理想値からのシフトを算出した。

Fig.1 C-V characteristics of the MOS capacitor.

フラットバンド電圧は理想的には SiO<sub>2</sub> 上電極に用いた金属と Si の仕事関数差で表される。今回作製した MOS キャパシタのフラットバンド電圧と理想値との差は 3.9V であった。これは酸化膜中における固定電荷の存在が原因と考えられる。

最後に  $SiO_2/Si$  界面における界面準位密度を算出したところ、 $4.3\times10^{13}[states/cm^2]$ となった。界面準位密度は低周波 C-V 特性と高周波 C-V 特性を用いて High-Low 法<sup>1)</sup>により算出した。今回作製したMOSキャパシタにおいては、界面準位低減のための  $H_2$  アニールなどの処理は行っていないために、比較的多量の界面準位が存在すると考えられる。

#### 4. その他・特記事項 (Others)

[1] R.Castagne and A.Vapaille, Surface Sci., 28. 157 (1971)

# 5. 論文・学会発表 (Publication/Presentation) なし。

## 6. 関連特許 (Patent)

なし。