※課題番号 : F-12-UT-0133

\*\*支援課題名(日本語) : 新規センサを目指す CMOS-MEMS 集積化技術

\*\*Program Title (in English) : CMOS-MEMS Integration Technology for Future Sensors

※利用者名(日本語) : 関口亮太

\*Username (in English) : Ryota Sekiguchi

※所属名(日本語) : キヤノン株式会社・総合 R&D 本部

\*\*Affliation (in English) : Canon Inc.

## <u>\*\*概要(Summary)</u>:

東京大学 VDEC がナノプラットで提供する CMOS マルチチップウエーハと、キヤノンによる高周波用センサ素子とを融合した、新規センサを作製する。共同研究によって実施し、初年度はクリーンルーム関係の利用手続きならびに問題点の洗い出し、サンプル VLSI 回路の特性測定を行った。

## \*\*実験 (Experimental):

キヤノン株式会社では、次世代の高周波センサ向けの新規素子の研究を行っている。これまで自社内の開発で、基幹部品である単体の検出素子プロセスが固まってきたので、システムとしての性能検証の段階として、素子の近傍で情報処理(増幅、レベル変換、アドレッシング等)を行うために、大規模集積回路(VLSI)と集積化したいと考えている。

具体的には、トランジスタ回路を作製したシリコンウエーハを受け取り、社内ならびに東京大学微細加工拠点でポストプロセス加工を行い、テストデバイスを作製する。

このような研究が行える場所を調査したところ、東京大学大規模集積システム設計教育研究センター (VDEC)が、1996年より集積回路の相乗り試作を行ってきており、その知見をもとに、受入元の研究室が中心となってナノテクノロジープラットフォーム事業として、6インチウエーハで設計した回路を受け取れる相乗り試作を行っていることがわかり、共同研究を行うこととした。

#### \*\*結果と考察(Results and Discussion):

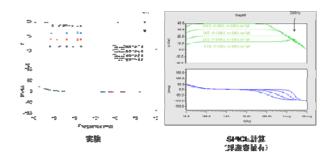

一年目の成果物として、「①あらかじめ作製した CMOS 回路のポストプロセス工程との整合性」なら びに、「②増幅回路のスタンダードセル検討」があり、 ①については、大規模集積システム設計教育研究セン ターの設計環境を用いてテスト構造を設計している。②については、基本回路の演算増幅器を評価した。具体的には、ナノプラット試作によって得られた6インチウエーハを、ステルスダイシング装置によってチップに分割し、基板加工機で作製した測定用専用ベース基板に接着した後、ワイヤボンディング装置によって配線を行った(図1)。測定用の受動部品を追加し、発振器とオシロスコープに接続して特性を評価した。結果をSPICEシミュレーションと比較し、結果が一致した(図2)。

#### ※その他・特記事項 (Others):

なし

## 共同研究者等(Coauthor):

尾内敏彦(総合 R&D 本部、研究室長)

坂本直之(東京大学三田研)

米田圭祐 (東京大学三田研)

三田吉郎 (東京大学大学院工学系研究科)

# <u>論文・学会発表(Publication/Presentation)</u>:

なし

図1: VDEC で作製した VLSI 回路チップ

図2:増幅回路のボーデ線図(ゲイン4種)