\*\*課題番号 : F-12-NM-0048

※支援課題名(日本語):選択成長ナノグラフェン薄膜を用いた電界効果型トランジスタの作成

\*Program Title (in English) : Preparation of graphene field-effect transistors by a selective-area

growth method

※利用者名(日本語): 石井 孝文

\*Username (in English) : Takafumi Ishii

※所属名(日本語):東北大学

\*\*Affiliation (in English) : Tohoku University

### \*\*概要 (Summary):

当研究室では  $Si/SiO_2$  基板上の  $Al_2O_3$  薄膜マイクロパターン表面にナノグラフェン薄膜を選択的に成長させることに成功しており、この手法を用いればナノグラフェン電子デバイスを簡便に作成できると考えられる。本研究ではこの選択成長ナノグラフェン薄膜を電界効果型トランジスタ(FET, Field Effect Transistor)として応用し、その評価を行った。

## \*\*実験(Experimental):

### 【利用した主な装置】

- ・マスクアライナー

- ・マスクレス露光装置(D-light, DL-1000/NS)

- ・E-gun 蒸着装置(RDEB-1206K)

- ・半導体パラメーターアナライザー (LN2 Prober)

- ・オートマチックスクライバー

【実験方法】 FET の作製は次の  $a \sim d$  の 4 工程によって行った。 (a) SiO<sub>2</sub>/Si 基板上にスパッタ  $Al_2O_3$  薄膜を形成。 (b) フォトリソグラフィーと液相エッチングによる  $Al_2O_3$  薄膜マイクロパターンの作成。 (c)  $Al_2O_3$  薄膜表面へのナノグラフェン薄膜の選択成長。 (d) フォトリソグラフィー、Au/Ti 電極の蒸着形成、リフトオフによるナノグラフェン薄膜上への電極形成。

以上のように作製した FET について、半導体パラメーターアナライザーを用いて、その FET 特性評価を行った。

### \*\*結果と考察(Results and Discussion):

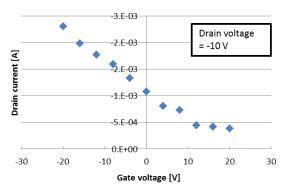

FET 特性評価を行った結果を Fig. 1 に示す。ナノグラフェン薄膜 FET の電気伝導度がゲート電圧により変化している様子が観察された。作製したナノグラフェン薄膜 FET はチャネル幅 20  $\mu$ m、長さ 2  $\mu$ m、ナ

ノグラフェン薄膜のナノグラフェン平均成長層数が 0.5 層である。ナノグラフェン薄膜の平均層数を 1 層以下にしたことで、薄膜中にナノグラフェンの単一チャネルが形成され、その量子サイズ効果によってバンドギャップが形成されたと考えられる。

Figure 1 Back-gate transfer characteristics of the nano graphene-FET.

### \*\*その他・特記事項 (Others):

今後の課題、予定:今回作製したグラフェン FET を センサーデバイスとして応用する試みを行なっていく。 共同研究者等 (Coauthor):

干川康人 A, 京谷隆 A, 岡井誠 B (A 東北大学, B 日立製作所)

# <u>論文・学会発表(Publication/Presentation)</u>:

Takafumi Ishii, Yasuto Hoshikawa, Takashi Kyotani, Makoto Okai, "Preparation of graphene field-effect transistors by a selective-area growth method", KJF2012 (Tohoku Univ.), PB37, 2012

Takafumi Ishii, Yasuto Hoshikawa, Takashi Kyotani, Makoto Okai, "Preparation of graphene field-effect transistors by a selective-area growth method", POSTECH - Seoul National University - Tohoku University Joint Symposium (Seoul National Univ.), SS2, 2013