課題番号 :F-12-AT-0048

※支援課題名(日本語) :シリコンフォトエレクトロニクスに関する研究

\*Program Title (in English) :Study of silicon photo-electronics

※利用者名(日本語) :宮崎哲男

\*\*Username (in English) : Tetsuo Miyazaki \*\*所属名(日本語) : 明治大学理工学部

\*\*Affliation (in English) : Meiji University, School of Science and Technology

#### ※概要(Summary):

光通信技術の発達に伴い、光デバイスの小型化が望まれている。そこで、本研究では半導体産業で培われた微細加工技術を応用し、低損失なシリコン細線光導波路作製プロセスの開発を行った。その結果、伝搬損失 1.25dB/cm の超低損失シリコン細線光導波路が実現された。さらに、高性能な光スイッチング素子を実現するため、この作製技術を応用してシリコン細線導波路型方向性結合器を作製したところ、消光比約 33dB を達成した。

#### <u>\*\*実験(Experimental)</u>:

利用した装置

- ・エッチング装置 ・短波長レーザ顕微鏡 ・触針段差計

- ・FE-SEM ・イオンコータ ・スピンコータ

- ・プラズマアッシャー・スクライバー・ダイシングソー

- ・プラズマ CVD ・i 線ステッパー

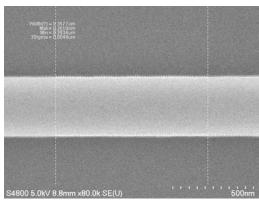

低損失なシリコン細線光導波路作成プロセスの確立のため、FE-SEM を使用して露光後のレジスト形状を観察した。FE-SEM に内蔵されている測長機能を使用し、レジストの側壁荒さ(ラインウィドスラフネス、LWR)を評価した。

エッチングや CVD を経てデバイスを完成させた。

## \*\*結果と考察(Results and Discussion):

20mm 四方の SOI 基板にパターニングされた幅 450nm 前後の光導波路レジストパターンを、基板上 方から FE-SEM で観察した (図 1)。露光条件が異なるサンプルを比較した。その結果、露光量と露光パターンを最適化することに成功した。

図 1 FE-SEM による LWR の評価

TEOS-CVD は NPF 標準のレシピで稼動し、約 1.8um の TEOS 膜を形成した。

完成したシリコン細線光導波路の伝搬損失は 1.25dB/cmであった。導波路幅が広いほど損失が低減さ れる傾向にあることが確かめられた。

#### \*\*その他・特記事項(Others):

本研究で確立したプロセスを利用し、方向性結合器の 試作も行った結果、消光比 33dB の良好なデバイスが得 られた。

今後の課題はTEOS-CVD 条件の最適化などがある。

# 共同研究者等(Coauthor):

受け入れ担当者:榊原陽一

(ナノエレクトロニクス研究部門シリコンフォトエレクトロニクス グループ)

#### 論文·学会発表(Publication/Presentation):

2012年度卒業論文

### 関連特許(Patent):

なし